第49回 56Gbps伝送技術:前田真一の最新実装技術あれこれ塾(5/5 ページ)

5.56Gbps

このように銅配線が多くの努力の積み重ねにより、つい数年前までは光でなければ不可能と思われていた10Gbpsの壁を破り、28G〜32Gbps程度の転送速度を実現しています。

今後もこのような努力により、32Gbps以上の速度を徐々に実現していくと思われます。

しかし、それは、素材や回路、方式などの改良により徐々に実現されるもので飛躍的な高速化が実現できるものではありません。しかし、2017年には400Gb イーサネットの規格化がマイルストーンとしてあり、それには40Gbpsのバックプレーンと基板上のデータ転送が含まれています。

2017年の規格化ということは、2015年には、40Gbpsのデータ転送が評価できる状況になければ、タイミング的に不可能です。実は、現在の28Gbps(14GHz)の転送技術を使って倍の58Gbpsのデータ転送を実現させるためのシステム検証が行われはじめています。

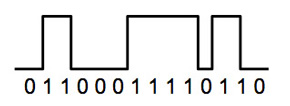

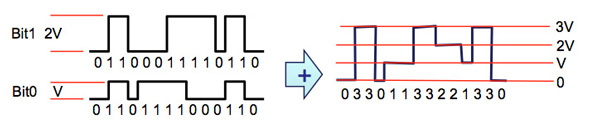

現在、シリアルデータ転送は「ハイ=1」と「ロー=0」のNRZ方式でデータを送っています(図7)。

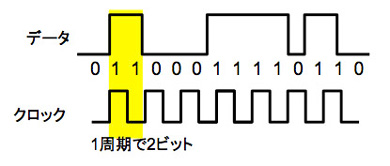

これは1/2クロックで、1ビットのデータが送れます(図8)。

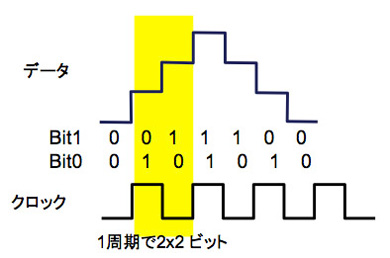

これを「V1=11」「V2=10」「V3=01」「V4=00」と信号の電圧を変化させることにより、1/2クロックで2ビットのデータを送れれば、14GHzで56Gbpsのデータが送れるようになります(図9)。

この4値によるデータ転送方式はPAM(Pulse Amplitude Modulation=パルス振幅変調)4と呼ばれ、既に100Gbイーサネットのケーブル伝送などに使われています(図10)。

しかし、2値に比べ、4値でのデータ転送にはいろいろな困難が伴います。

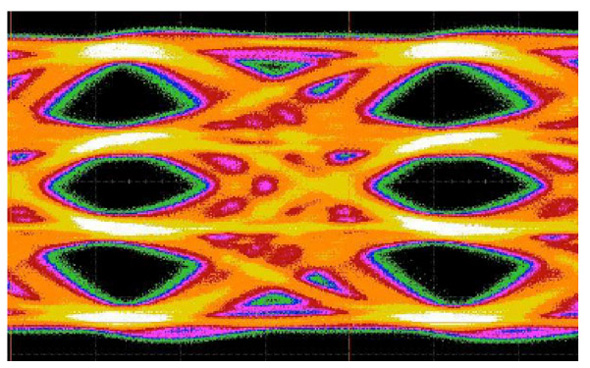

信号品質に対しても、2値であれば、Eyeの開口に対しては、多少のオーバシュートやアンダシュートは認められてきましたが、4値になると、中間値のオーバシュートやアンダシュートは他の値の開口を妨げます(図11)。

図11:PAM4のEye Pattern(E.Frlan, C.YeLiu, M.PengLi “Signal Integrity Challenges & Solutions for Next-Generation CEI-56G “Chip-to-Module” & “Chip-to-Chip” Interface, DesignCon 2015)

図11:PAM4のEye Pattern(E.Frlan, C.YeLiu, M.PengLi “Signal Integrity Challenges & Solutions for Next-Generation CEI-56G “Chip-to-Module” & “Chip-to-Chip” Interface, DesignCon 2015)当然、58Gbps転送のシステム検証は、単にデータが転送できることの検証ではなく、測定技術、ビットエラーレートをはじめとする、信頼性評価、測定技術やシミュレーション技術の確立、コンプライアンス試験の確立など多岐にわたり、時間もかかります。

現在、このような4値のドライバ回路やレシーバ回路は既にIC回路として実現されており、評価がはじまっています。

2値のNRZ方式の高速化、他のデータ圧縮技術、PAM4だけでなく、さらに多値化によるクロックを遅くしての転送方式なども視野に入れながら、データ転送の高速化が検討されています。

筆者紹介

前田 真一(マエダ シンイチ)

KEI Systems、日本サーキット。日米で、高速システムの開発/解析コンサルティングを手掛ける。

近著:「現場の即戦力シリーズ 見てわかる高速回路のノイズ解析」(技術評論社)

関連記事

- ≫前田真一の最新実装技術あれこれ塾

摩擦があると、どうしてエネルギーを失うのか

摩擦があると、どうしてエネルギーを失うのか

摩擦によって力学的エネルギーが損失することを理解するためには、まずニュートンの運動方程式をきちんと理解する必要がある。 SiC-MOSFETの課題克服へ、新材料を用いたゲート絶縁膜で信頼性を向上

SiC-MOSFETの課題克服へ、新材料を用いたゲート絶縁膜で信頼性を向上

SiC-MOSFETの量産採用に向けた課題の1つとして挙げられているのが、酸化シリコンを用いたゲート絶縁膜に起因する動作時の信頼性の低さだ。大阪大学と京都大学、ローム、東京エレクトロンは、AlON(アルミニウム酸窒化物)を用いたゲート絶縁膜によって、SiC-MOSFETの信頼性を高める技術を開発した。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 日本が再び世界をリードするための、“シン”モノづくりの世界

- 自動車工場で聞こえるのに、食品工場では聞こえない音〜工場の主人公は誰か

- 「自動車以外は全て好調」、四半期受注過去最高のDMG森精機が通期予想上方修正

- エンジニアリング業務を自律実行、シーメンスが産業AIを新たな段階に

- マグネットで触れるだけ、振動値を5秒で判定する回転機振動チェッカー

- 「ロボット大国」日本の逆襲、地道なモノづくりが世界を動かす交渉力に

- 猛暑に備えて

- 工場の主人公は誰なのかという問いかけ、元トヨタ生技が見た食品工場のなぜ

- ヒューマノイド中核部品がハノーバーメッセ技術賞、“脱自動車”のシェフラー開発

- 防衛事業の生産体制強化、ソナーなど水中音響センサーの新生産棟を建設

コーナーリンク

図7:MRZ転送方式

図7:MRZ転送方式 図8:1/2クロックで1ビットのデータ転送

図8:1/2クロックで1ビットのデータ転送 図9:4値でのデータ転送

図9:4値でのデータ転送 図10:PAM4変調

図10:PAM4変調