第50回 モジュールとエンベデッドパッシブ:前田真一の最新実装技術あれこれ塾(1/5 ページ)

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第50回はモジュールとエンベデッドパッシブについて解説する。

1.電源ノイズ

現在、ICや基板の設計で最も大きな課題は、電源です。

ICの集積度が上がり、高機能、高処理速度化が進むのに比例し、ICの消費電力が大きくなってきました。性能を向上させながら、消費電力を抑えることがIC設計の最大の課題となっています。

電源電圧を低くすることは、ICの消費電力を抑え、信号の高速化を計り、ノイズを抑えることにも、全てに対して有効な方法です。このため、ICの電源電圧は定電圧化が進み、現在は1.0Vや0.8Vなどまで下がってきています。

メモリでもDDRメモリでは2.5Vであったものが、DDR2では1.8V、DDR3では1.5Vになり、最新のDDR4では1.2Vになっています。電源電圧が下がると、ICに供給する電源の品位も高いものが要求されます。

電源電圧が5Vや3.3Vの時は、電圧許容誤差範囲は±10%でした。5Vでは±500mVまで許されていたのです。

これが、1.8Vや1.5Vでは±5%と許容誤差が半分になり、1.0Vでは±3%とさらに厳しくなりました(表1)。電源電圧が30mV以上変動したら、LSIが正常動作しなくなるのです。

基板設計で、これだけ安定した定電圧をICに供給するような設計をすることは、相当に難易度が高くなります。特にIC内部のトランジスタの多くがクロックに同期したタイミングでオン/オフするときにICに大きな電流が流れます。電源電圧が急激に低下する際のノイズは大きなトラブルとなります。

電源回路は定電圧源で常に一定の電圧をICに供給しています。

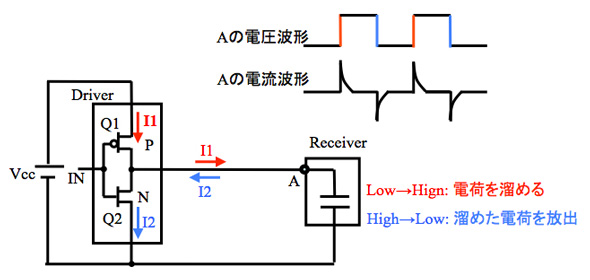

IC内部のCMOS回路は信号がハイかロー状態の時は非常にインピーダンスが高く、ほとんど電流が流れませんが、ローからハイへ信号が変化(スイッチング)するときにはレシーバのトランジスタが持つ小さな容量(C)に電流が流れ込みます(図1)。

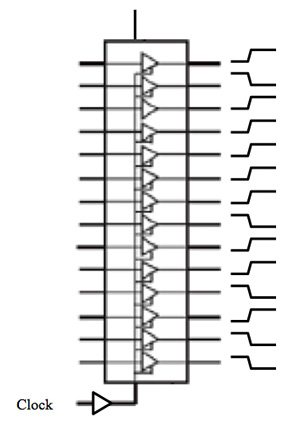

容量は非常に小さいので、1つ1つでは流れる電流は小さいのですが、クロックに同期して多くのトランジスタが同時にスイッチングするので、IC全体では、急激に大きな電流が流れます(図2)。

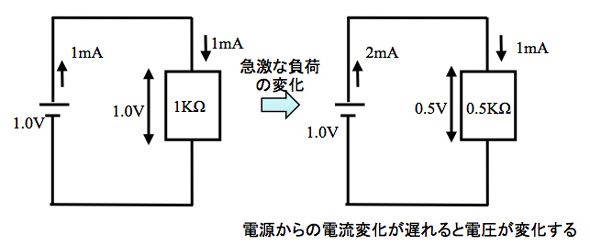

定電圧電源は負荷の変化に応じて、供給する電流をコントロールし電圧の負荷を一定にします。しかし、ICの内部回路が高速化し、負荷のインピーダンス変化が高速になると、電源回路からの電流変化が負荷の変化に追い付かなくなります。

負荷のインピーダンスが変化してから、電源の電流対応が届くまで、インピーダンスが低下して、それに対応した電流が増加するまでの間に電源電圧も低下します(図3)。

これが同時スイッチング(SS)ノイズと呼ばれるノイズで、ICの電源電圧が変動します。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 自動車工場で聞こえるのに、食品工場では聞こえない音〜工場の主人公は誰か

- 「ロボット大国」日本の逆襲、地道なモノづくりが世界を動かす交渉力に

- エンジニアリング業務を自律実行、シーメンスが産業AIを新たな段階に

- 猛暑に備えて

- マグネットで触れるだけ、振動値を5秒で判定する回転機振動チェッカー

- 工場の主人公は誰なのかという問いかけ、元トヨタ生技が見た食品工場のなぜ

- 防衛事業の生産体制強化、ソナーなど水中音響センサーの新生産棟を建設

- ヒューマノイド中核部品がハノーバーメッセ技術賞、“脱自動車”のシェフラー開発

- 「自動車以外は全て好調」、四半期受注過去最高のDMG森精機が通期予想上方修正

- アジア系投資ファンドが牧野フライスTOB中止、日本産業推進機構が初期提案

コーナーリンク

表1:DDRメモリの電源電圧と変動許容

表1:DDRメモリの電源電圧と変動許容 図1:CMOS回路と消費電流

図1:CMOS回路と消費電流 図2:多くのドライバが同時にスイッチングする

図2:多くのドライバが同時にスイッチングする 図3:電流の供給が遅れると電圧が降下する

図3:電流の供給が遅れると電圧が降下する