第43回 PCI Express Gen4:前田真一の最新実装技術あれこれ塾(1/5 ページ)

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第43回はPCI Express Gen4について解説する。

本連載は「エレクトロニクス実装技術」2014年10月号の記事を転載しています。

1.高速シリアルリンク

2014年6月に「PCI Express」の規格を作成しているPCI-SIGが主催するPCI-SIG Developers Conference 2014がアメリカのサンタクララ・コンベンションセンターで開催されました。

ここで、ここ数年話題になっていた「PCI Express Gen4」についての技術が発表されました。

このPCI Express Gen4は現在、技術評価もほぼ終わり、2014年年末から2015年の前半に規格を発表する予定になっています(「エレクトロニクス実装技術」2014年10月号発行時点)。

この新しい規格について説明する前に、PCI Express規格について簡単に説明します。

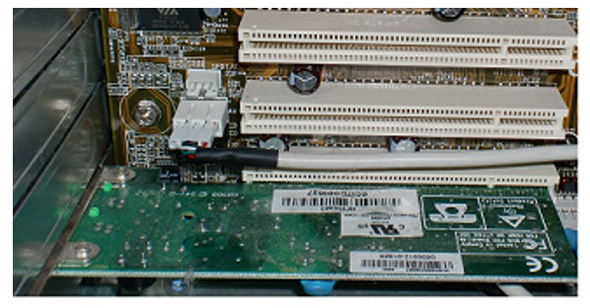

PCI Expressは2002年にPCI-SIGによって最初の規格Gen1が発表されたバス規格です。1991年にインテルが発表したPCIバスは32/64ビットのデータを並列で転送する並列データバスで、ほぼ全てのコンピュータに採用されました(図1)。

PCIバスは転送速度を上げたり、5.0Vロジックから3.3Vロジックに電圧を拡張したりしたことで、1.0から3.0までバージョンアップしました。またさらに高速化したPCI-X規格も策定されました。

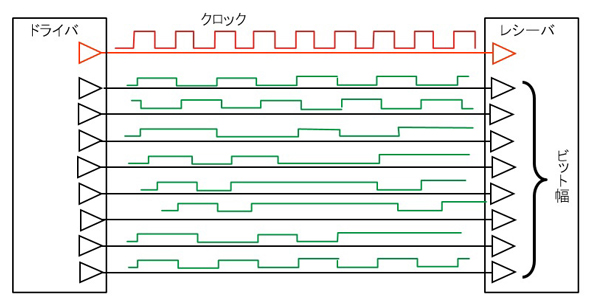

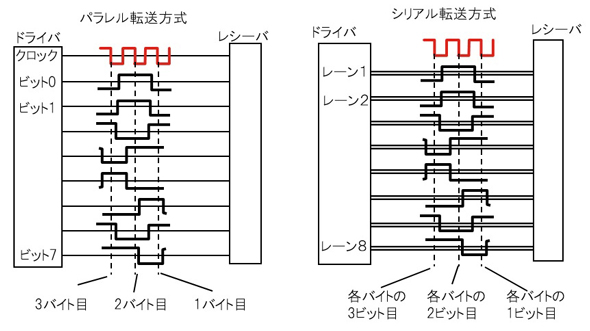

しかし、多くの並列データを同期させて転送する並列転送バスではデータの同期が困難で、高速化が頭打ちになってしまいました。バスの転送速度はクロック速度と1クロックで並列に転送するビット幅の積になります(図2)。

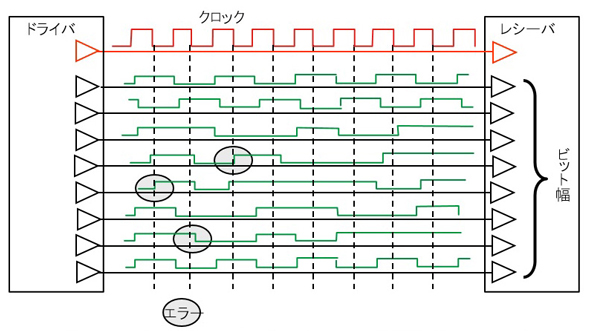

高速並列バスでは、ビット幅を大きくすると、同期を取るためにクロック速度を下げなければなりません。また、クロック速度を上げるためには、ビット幅を少なくしなければなりません(図3)。

結果として、並列バスでは、これ以上の高速化対応が困難になってなってしまいました。メモリバスは並列で非常に高速ですが、これは4/8ビットと比較的に小さいビット数で転送しています。しかもメモリバスは配線をできるだけ短くして配線しています。

しかし、どのようなコンピュータやインタフェースカードに接続される汎用データバスでも、規格で配線長さを短く制限してしまっては、設計が難しくなり、規格が普及しません。このため、配線長の制限を緩和し、誰でも安い基板を作れるような規格にする必要があります。

並列バスのデータ転送速度が誰でも設計、製造できる条件で、これ以上高速化するのが困難になり、直列転送方式が浮上しました。

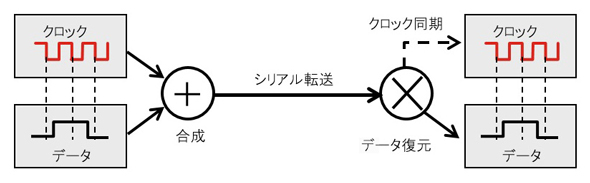

新しい直列転送方式ではデータとクロックを変調をかけて同じ1ビットで送り、受け側で、データからクロックを生成し同期を取ってデータを受信します(図4)。このため、非常に高速にデータを転送することができます。

実際、並列バスのPCI-Xバスでは133MHzのクロックでしたが、少し前に規格化された直列の「PCI Express Gen1」では1.25GHzで、10倍近い速度になっています。しかし、並列バスでは8ビット並列で同程度、16ビット並列にすれば、直列転送方式よりも早くデータが転送できます。このため、PCI Expressでは直列伝送回路(「レーン」と呼びます)を4本・8本・16本と並列に並べ、転送速度を高速化しています。

例えば、8ビットの並列バスと8レーンの直転送を比べてみます。8ビットの並列バスでは1クロックで1バイト(8ビット)のデータが送れます。8クロックでは8バイトのデータが送れます(図5)。

8レーンの直列バスでは1クロックでは8つのデータの最初の1ビットだけ送られ、バイトデータの転送は終わっていません。8クロック目のデータが送られてはじめて、8レーンのデータにおのおののバイトデータの転送が終了します。

つまり、直列方式では、8クロック単位でで8バイトのデータを送ります。並列バスはリアルタイム転送ですが、直列転送はパケット転送になります。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 日本が再び世界をリードするための、“シン”モノづくりの世界

- 自動車工場で聞こえるのに、食品工場では聞こえない音〜工場の主人公は誰か

- 「自動車以外は全て好調」、四半期受注過去最高のDMG森精機が通期予想上方修正

- エンジニアリング業務を自律実行、シーメンスが産業AIを新たな段階に

- なぜオムロンは農業の“作業”ではなく“判断”の自動化を目指すのか

- 「ロボット大国」日本の逆襲、地道なモノづくりが世界を動かす交渉力に

- マグネットで触れるだけ、振動値を5秒で判定する回転機振動チェッカー

- 猛暑に備えて

- 工場の主人公は誰なのかという問いかけ、元トヨタ生技が見た食品工場のなぜ

- ヒューマノイド中核部品がハノーバーメッセ技術賞、“脱自動車”のシェフラー開発

コーナーリンク

図1:PCIバス

図1:PCIバス 図2:バスの転送速度はバス幅とクロック速度の積

図2:バスの転送速度はバス幅とクロック速度の積 図3:クロックが早いとデータのタイミング誤差がエラーになる

図3:クロックが早いとデータのタイミング誤差がエラーになる 図4:クロックとデータを合成して送受信

図4:クロックとデータを合成して送受信 図5:シリアルとパラレルの違い

図5:シリアルとパラレルの違い