第43回 PCI Express Gen4:前田真一の最新実装技術あれこれ塾(3/5 ページ)

3.PCI Expressの技術

表1の規格を理解していただくためにも、ここで簡単にPCI Expressで使われている技術について説明します。

3-1.トポロジー

PCIバス、PCI Expressは3種類のトポロジー(配線形体)を想定しています。

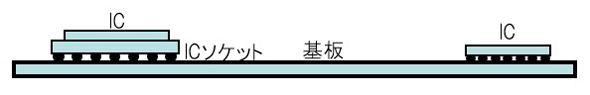

まずは同一基板内での配線です(図6)。

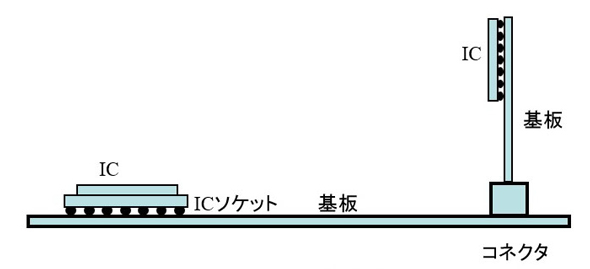

次は外部装置とのインタフェース基板など、サブ基板との接続を想定した、1コネクタ接続です(図7)。

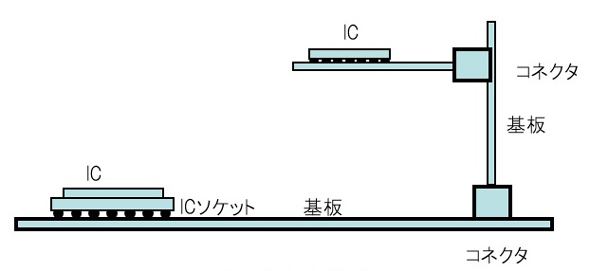

最後は、バックプレーンなどを介して基板間を接続する2コネクタ接続です(図8)。

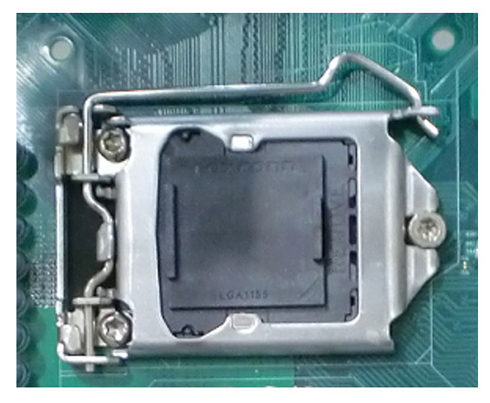

また、クライアントICは基板にはんだ付けを想定していますが、CPUチップなどホスト側ではソケットを使うことを許しています(図9)。

3-2.LVDSと差動配線

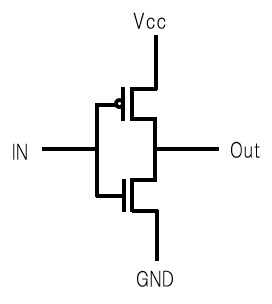

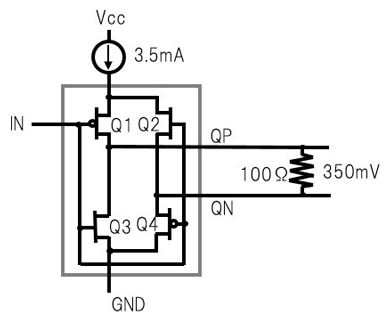

PCI Expressの回路には、一般の回路に使われているCMO回路(図10)とは違い、LVDS(Low Voltage Differential Signaling)と呼ばれる回路を使います(図11)。

このLVDS回路は常に一定の電流(3.5mA)を流していてレシーバ側の100Ωの終端抵抗で、350mVの電圧を発生するようになっています。

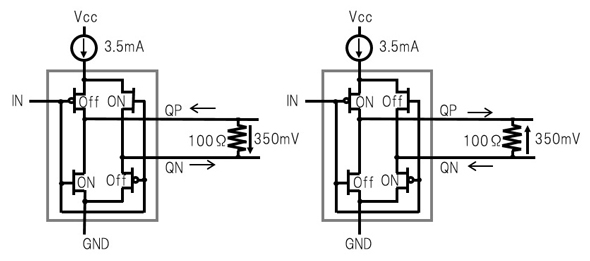

信号のHigh/Lowの切り替えは電流の方向を切り替えます(図12)。

理論的には、常に一定の電流を流しているので、信号のHigh/Low切り替えの時でも消費電流の変化がなく、同時スイッチングノイズが発生しません。

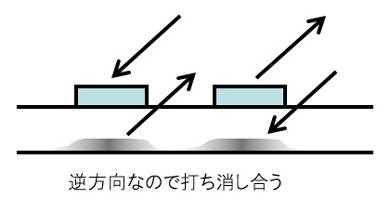

また、差動信号間で信号ループが完了します。差動信号を同じ層に平行して配線することにより、プレーンに流れるリターン電流もお互いに打ち消し合い、安定した信号伝送ができます(図13)。

3-3.クロック・リカバーと8-10変換

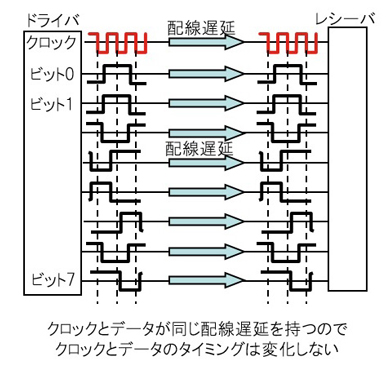

並列バスでは並列データと同時にクロック信号を送っています。このクロック信号でデータの同期を取ることにより、配線遅延の影響なしでデータのやりとりができます(図14)。

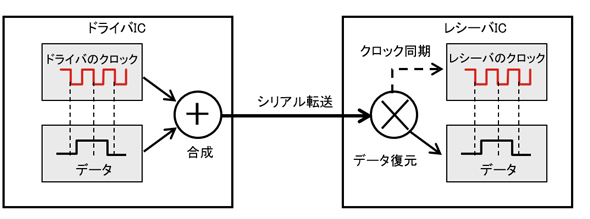

PCI Expressをはじめとするシリアル転送方式では、配線を少なくするために信号にクロックを埋め込んで、信号とクロックを1組(差動なので2本)の信号配線で送っています。

クロックはドライバ側とレシーバ側でおのおの独自に持っています(図15)。

レシーバ側ではデータを受け取るとデータの立ち上がり/立ち下がりエッジに合わせてクロック信号のずれを直して、受信データに自分のクロックを同期させ、このクロックでデータを読み込みます(図16)。

このレシーバ側で受け取ったデータに合わせてクロックの同期を調整することを「クロックリカバー」と呼びます。

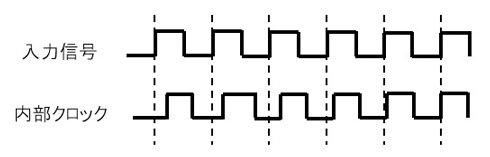

データとクロックを同期させるためにはデータ信号のハイ/ローの変化でエッジを検出する必要があります。

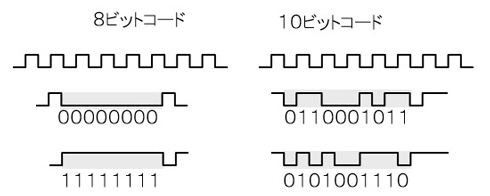

現在、データ転送にはNRZ(Non Return Zero)方式と呼ばれる方法を取っています。これは、0000とか1111などのように、データが変化しないと信号もロー・ロー・ローなど同じデータが連続して、信号の変化が少なくなります。

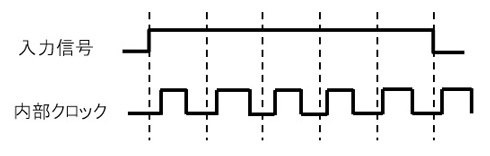

データが全て0であったり、全て1であったりするとデータが変化しないので、クロックの同期がずれる場合があります(図17)。

このため、8ビットのデータを10ビットのデータに変換して、0や1のデータが長く連続しないようにします。これを「8-10変換」と呼びます(図18)。

8-10変換を行うと1バイト(8ビット)のデータを転送するのに10クロックが必要となります。

この8-10変換はPCI Express Gen1とGen2で使われましたが、Gen3が発表される頃にはクロックリカバー回路の精度が向上して、ハイ/ローの変化が少なくてもクロックの同期ズレが起こりにくくなりました。このため、クロックの周波数を下げる目的で、8−10変換をやめて、128ビットに対して2ビットを付加する128−130ビット変換を行うようになりました。

このため、Gen3以降は1バイトのデータを転送するには8クロックでよくなりました。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 日本が再び世界をリードするための、“シン”モノづくりの世界

- 自動車工場で聞こえるのに、食品工場では聞こえない音〜工場の主人公は誰か

- 「自動車以外は全て好調」、四半期受注過去最高のDMG森精機が通期予想上方修正

- なぜオムロンは農業の“作業”ではなく“判断”の自動化を目指すのか

- エンジニアリング業務を自律実行、シーメンスが産業AIを新たな段階に

- マグネットで触れるだけ、振動値を5秒で判定する回転機振動チェッカー

- 「ロボット大国」日本の逆襲、地道なモノづくりが世界を動かす交渉力に

- 工場の主人公は誰なのかという問いかけ、元トヨタ生技が見た食品工場のなぜ

- 猛暑に備えて

- ヒューマノイド中核部品がハノーバーメッセ技術賞、“脱自動車”のシェフラー開発

コーナーリンク

図6:同一基板内での接続

図6:同一基板内での接続 図7:1コネクタ接続

図7:1コネクタ接続 図8:2コネクタ接続

図8:2コネクタ接続 図9:ICソケット

図9:ICソケット 図10:CMOS回路

図10:CMOS回路 図11:LVDS回路

図11:LVDS回路 図12:LVDS回路動作

図12:LVDS回路動作 図13:差動信号のリターン電流

図13:差動信号のリターン電流 図14:クロックとデータは同期

図14:クロックとデータは同期 図15:ドライバとレシーバは、おのおの独自のクロックを持っている

図15:ドライバとレシーバは、おのおの独自のクロックを持っている 図16:レシーバの内部クロックを入力信号に同期させる

図16:レシーバの内部クロックを入力信号に同期させる 図17:入力データが変化しないと内部クロックとデータの同期が取れない

図17:入力データが変化しないと内部クロックとデータの同期が取れない 図18:8-10変換

図18:8-10変換