第49回 56Gbps伝送技術:前田真一の最新実装技術あれこれ塾(4/5 ページ)

4.損失対策

1の材料の工夫は、誘電損失と抵抗損失の両面から、できる限り進められています。

まず、誘電損失の大きさは絶縁体の誘電率(ε)と誘電正接(tanδ)の2つの特性で決まります。このため、高速信号用の基板では、誘電率と誘電正接が比較的大きいFR-4から小さい低損失材料への変更がされています。

現在、より損失の小さいレジンやガラスクロスの開発が素材メーカーでいろいろと試行されています。

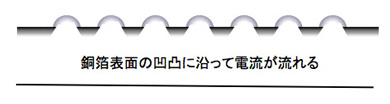

抵抗損失は表皮効果によるもので、銅配線の表面粗さが大きいと、損失が大きくなります(図2)。

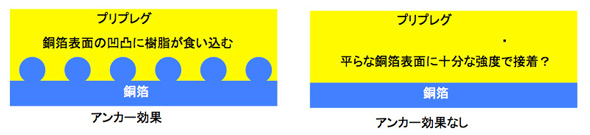

このため、銅箔表面をできるだけスムーズにすると同時に、アンカー効果がなくとも銅箔と基材との接着強度が保てるような接続技術についても開発が進められています(図3)。

しかし、これらの新素材や新技術はいきなり出てくるわけではなく、地道な開発により、少しずつの進歩が出てくるものです。

2の回路についても、いろいろなアイデアや回路とソフトの実現で少しずつ改善が進められています。

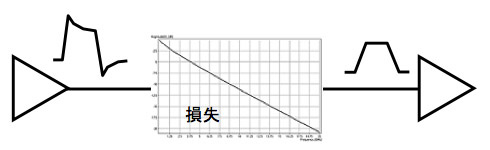

ドライバ側では損失の大きな高い周波数成分だけを増幅するために使われるプリエンファシス回路があります(図4)。

しかし、ドライバの出力信号を大きくすることは、信号の電力を大きくすることなので、消費電力の増大、同時スイッチングノイズや電磁放射ノイズの増大につながります。また、出力信号の信号電圧をドライバの電源電圧以上に高くすることはできません。

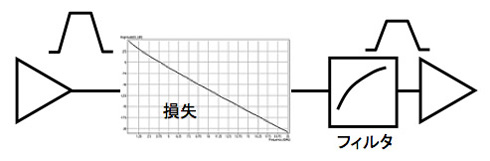

レシーバ側では微弱な信号を損失の大きさに応じて増幅させるためのフィルター回路があります(図5)。

損失は配線長さや、基板材料、ビアの数などによって異なります。このため、ドライバやレシーバの回路特性はシステム立ち上げ時にドライバとレシーバがテスト信号のやりとりを行いながら最適な特性を決定するようにしています。

また、信号の同期も初期には8bit‐10bit変換を使っていましたが、現在は、より進歩した同期を使い、データ伝送周波数(GT/s)がそのままデータ転送速度(Gbps)になるようにしています。

3についての対応には文字通り、配線を短くする方法とリピータがあります。

損失は配線長さに比例しますから、短い配線では、小さくなります。

このため、基板内配線では、できるだけ高速信号の配線を短くすることにより、損失を小さくすることができます。

バックプレーンなど長い配線が必要な場合には、配線の途中にリピーターを挿入する事が考えられます。

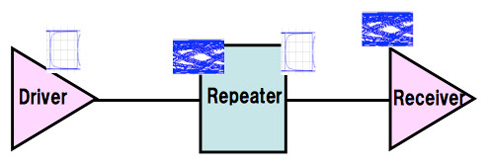

リピータはレシーバとドライバを持った回路で、損失で減衰した信号を整形、同期ずれの修復、増幅して、新たなドライバ信号として出力します(図6)。

高速伝送線路解析用のIBIS AMIでもこのリピーターのある回路の解析ができるようになっています。

しかし、リピーターを挿入するとバックプレーンの設計やコストアップになるので、光伝送との競合の可能性もあります。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 日本が再び世界をリードするための、“シン”モノづくりの世界

- 自動車工場で聞こえるのに、食品工場では聞こえない音〜工場の主人公は誰か

- 「自動車以外は全て好調」、四半期受注過去最高のDMG森精機が通期予想上方修正

- エンジニアリング業務を自律実行、シーメンスが産業AIを新たな段階に

- マグネットで触れるだけ、振動値を5秒で判定する回転機振動チェッカー

- 「ロボット大国」日本の逆襲、地道なモノづくりが世界を動かす交渉力に

- 猛暑に備えて

- 工場の主人公は誰なのかという問いかけ、元トヨタ生技が見た食品工場のなぜ

- ヒューマノイド中核部品がハノーバーメッセ技術賞、“脱自動車”のシェフラー開発

- 防衛事業の生産体制強化、ソナーなど水中音響センサーの新生産棟を建設

コーナーリンク

図2:銅箔の表面粗さと表皮効果

図2:銅箔の表面粗さと表皮効果 図3:アンカー効果がなくても接着力を向上

図3:アンカー効果がなくても接着力を向上 図4:ドライバのプリエンファシス

図4:ドライバのプリエンファシス 図5:レシーバのフィルタ

図5:レシーバのフィルタ 図6:リピータ

図6:リピータ