第10回 LSIの消費電力:前田真一の最新実装技術あれこれ塾(3/3 ページ)

3. 低電力設計

メモリの低電力化についてはモバイルDDRとして、規格化が進んでいます。

CPUについては基本的な共通の技術を使い低消費電力化を図るとともに、各CPUベンダーがおのおの、独自のアプローチから、低電力化の努力をしています。基本的な技術としては、電源電圧(コア電源電圧)の低電圧化と、マルチコア化、クロックの低速化などがあります。

どのようなICでも、電源電圧降下は消費電力の低減に大きな効果があります。しかし、現在の論理回路の基本回路となっているCMOSでは回路が動作するためには電源電圧の低減には限界があります。動作電圧をどこまで下げられるか、動作しない回路の電圧はどこまで、どのように下げられるか、CPUベンダー各社の独自技術となっています。

各社、単にCPUのコア電源電圧をどこまで、低電圧化させるだけではなく、CPUの処理量が小さい時や、待機状態時など、CPUの状態に応じて電源電圧を細かく制御するには、各社が独自の技術を使っています。

携帯電子機器では、動作時の低消費電力低減も重要ですが、待機時のバッテリーの持ち時間が重要な要素となります。待機時では、基本的に必要最低限の回路だけを必要最低限の電圧で動作させることにより、消費電力を可能な限り削減します。待機状態では回路が動作できる電圧でクロックを低速化してかろうじて動作さておき、動作状態に素早く復帰できるようにしておく必要があります。

待機状態で、少ない回路をできるだけ遅く動作させて待機しておけば、動作状態への復帰に時間がかかり、処理が遅いといわれます。多くの回路をある程度に速度で待機させていた場合には、復帰時間は速いのですが、待機状態でも電力を多く消費してしまいます。待機電力を小さくし、かつ復帰時間を短くする工夫は、CPUベンダーの回路技術とソフトウェアに依存します。

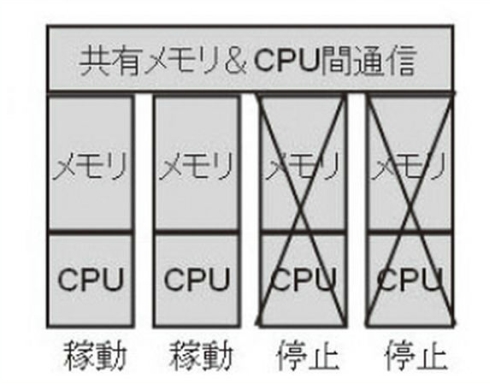

マルチコアCPUはシングルコアCPUに比べると、省電力設計が比較的簡単にできます。データ処理が多い場合にはすべてのコアを使って最大パフォーマンスで処理を行いますが、データの処理量に応じて、動作させるコアの数を減らすことにより、消費電力を低減することができます。さらに動作しないコアに対しては、クロック速度を下げたり、供給電圧を低下させたりして、より一層の電力低下が図れます。

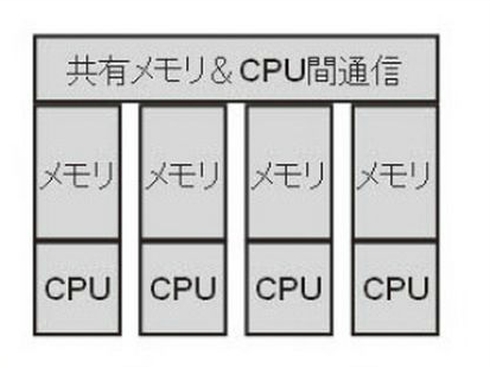

マルチコアCPUでは複数の全く同じコアが一つのICチップにレイアウトされており、各コア間にはコア間でデータや情報の通信を行うための配線が行われています(図8)。

このコア間通信の回路を工夫すれば動作していないコアの電源を落としてしまうことも可能です(図9)。

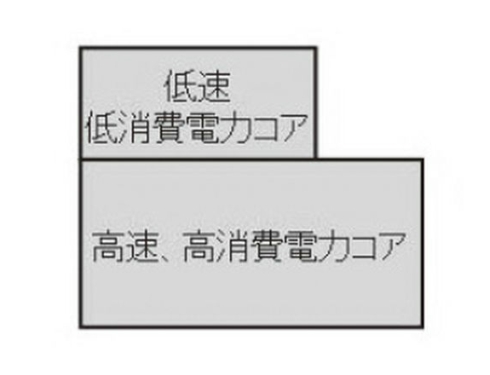

携帯電子機器では、動作時の低消費電力低減も重要ですが、待機時のバッテリーの持ち時間が重要な要素となります。CPUベンダーによって異なる低消費電力対策のアプローチも、いろいろな独自の手法が考えられています。例えば、電力消費が大きく、高速処理できるMPUと処理能力は劣るが、消費電力が小さなMPUのマルチコアチップを使い、処理量に応じてコアを使い分ける技術を開発しているCPUベンダーもあります(図10)。

このようにすると単純に同じコアを複数搭載したマルチコアCPUより、効率的に負荷にあわせた消費電力制御が可能となります。

このようにメモリやMPUの省力設計は具体的なアプローチが出てきました。ここ数年で、携帯機起用のMPUやメモリの消費電力は、たぶん性能向上による消費電力増大よりも大きくなると期待されています。

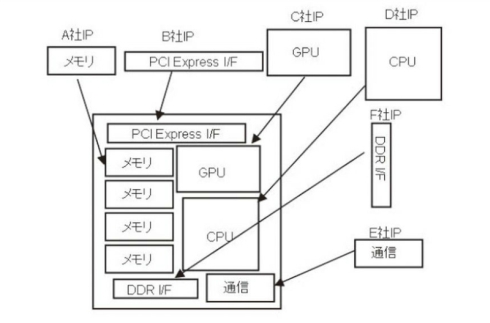

しかし、現在の電子機器、特にモバイル電子機器では、特に汎用のMPUなどはあまり使われてはいません。消費電力の低減と部品の小型化を目的に、大部分の機器では、MPUだけではなくインタフェースや周辺回路や部品を1チップ化した高機能ASIC(システムLSI)が使われています。例えば、ARMのMPUは単体のMPUチップとしての商品化はなく、IP(Intellectual Property)としてASICに組み込んで使う組み込み用MPUとして使われています。そもそも、ARM自体が組み込み用として開発されています。このほか、x86系のコアや多くのMPUがIPとして組み込み用に用意されています。

ここで問題となるのは、システムLSIと呼ばれるASICです。システムLSIではARMを始めとするMPUやDDRメモリやSDRAMなどを接続するメモリインタフェース、PCI Expressやビデオインタフェースを始めとして、多くの機能回路ブロックをIPと呼ばれるブロックを組み合わせて1チップ化されています。いわゆるSoC(System on Chip)です。このIPと呼ばれるICの回路ブロックは多くの設計会社が設計し、流通しています。システムICベンダーはこれらのIPを組み合わせて1つのシステムICにまとめ上げます(図11)。

特に携帯機器では、部品点数を減らして、機器を小型化すると同時に消費電力を減らすためにASICを使い回路の大部分を1チップ化しています。

このASICの消費電力を減らすことが機器の低消費電力化への最大のテーマになっています。

ASICの消費電力低減に対しては、設計ツールを主に多くのアプローチが行われています。

筆者紹介

前田 真一(マエダ シンイチ)

KEI Systems、日本サーキット。日米で、高速システムの開発/解析コンサルティングを手掛ける。

近著:「現場の即戦力シリーズ 見てわかる高速回路のノイズ解析」(技術評論社)

関連記事

第9回 TSVを前提としたモバイルDDR

第9回 TSVを前提としたモバイルDDR

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第9回は、モバイルDDRメモリの最新規格である、LPDDR3と、第3回で取り上げたTSVによって実現可能になったWide IOについて解説します。 第8回 モバイルDDR

第8回 モバイルDDR

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第8回は、スマートフォンをはじめ、モバイル機器の高度化によって需要が拡大しているモバイルDDRメモリについて説明する。 第1回 DDR4

第1回 DDR4

「実装が新しい技術の普及を左右している――」。実装技術の専門誌「エレクトロニクス実装技術」で好評連載中の前田真一氏がMONOistに登場。実装分野の最新技術を分かりやすく紹介する。第1回のテーマは、次世代メモリ「DDR4」だ。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 日本が再び世界をリードするための、“シン”モノづくりの世界

- 自動車工場で聞こえるのに、食品工場では聞こえない音〜工場の主人公は誰か

- 「自動車以外は全て好調」、四半期受注過去最高のDMG森精機が通期予想上方修正

- エンジニアリング業務を自律実行、シーメンスが産業AIを新たな段階に

- なぜオムロンは農業の“作業”ではなく“判断”の自動化を目指すのか

- 「ロボット大国」日本の逆襲、地道なモノづくりが世界を動かす交渉力に

- マグネットで触れるだけ、振動値を5秒で判定する回転機振動チェッカー

- 猛暑に備えて

- 工場の主人公は誰なのかという問いかけ、元トヨタ生技が見た食品工場のなぜ

- ヒューマノイド中核部品がハノーバーメッセ技術賞、“脱自動車”のシェフラー開発

コーナーリンク

図8 マルチコア

図8 マルチコア 図9 マルチコアの一部停止

図9 マルチコアの一部停止 図10 2種類のプロセッサを使い分ける

図10 2種類のプロセッサを使い分ける