第10回 LSIの消費電力:前田真一の最新実装技術あれこれ塾(1/3 ページ)

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第10回は、モバイル機器向けでは特に重視される、MPUやシステムLSIの消費電力について解説します。

本連載は「エレクトロニクス実装技術」2012年1月号の記事を転載しています。

1. LSIの消費電力が問題

モバイルDDRでは消費電力の低減と、大容量、高速という能力向上との矛盾する要求に応えるために新しい技術を導入しています。この事情は、メモリを使うMPUでも全く同じです。

現在、ICの集積度の向上によるICの消費電力の増大は最大の問題になっています。特に、電池駆動のスマートフォンやタブレット端末などの携帯機器では機能向上とバッテリーの持続時間延長という相反する要求があります。

機能向上のためには搭載するCPUの処理能力を高め、より多くのメモリを使う必要があります。しかし、携帯機器ではバッテリーの駆動時間は大きな性能の要素になっています。バッテリーの容量増加による駆動時間増加のアプローチはありますが、バッテリー自体の技術革新による、容量増加は、ICの消費電力増加に追いつきません。バッテリーを多く積めば、機器の重量と体積が増加して、これも小型軽量化という重要な性能への影響が大きくあります。最近では、特に携帯機器ではMPUやシステムLSIの選択の第一条件は消費電力になっています。

さらに、大規模サーバでも電力事情から、消費電力に関心が高まり、低電力MPUが求められています。このため、IC開発の重点は高速化が最大の目標であったものが、省電力化に移ってきています。

現在、MPUチップでは、これまで言われてきたMIPS(Million Instructions Per Second)やFLOPS(Floating-point Operations Per Second)などといった、1秒間にどれだけの処理能ができるかの単純な処理能力から、1W当たりの処理能力に指針が移ってきています。

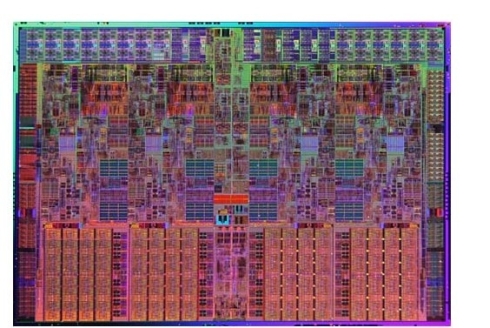

例えば、CPUは一時代前までは、速度競争をしていました。クロック速度がCPUの性能の尺度として使われてきました。しかし、ここ数年、クロック周波数はわずかしか延びていません。それに変わり、処理能力向上のために、マルチプロセッサ(マルチコア)化が進んでいます(図1)。これは、ICの集積度が上がり、複数のコアを1チップに集積できるようになったためだけではありません。高速化による消費電力の飛躍的増大を抑えながら、CPUの高速化を図る手法なのです。

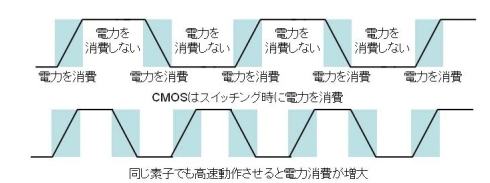

現在の論理素子の基本となっているCMOS回路は、高速になると飛躍的に消費電力が増大します(図2)。CPUクロックの高速化は単にCPUチップの消費電力を増大させるだけではありません。CPUが高速化されると、CPUに接続されているメモリをはじめ、あらゆる素子も高速化を要求され、システムとしては、非常に大きな消費電力の増大になります。

CPUのマルチコア化はコアの数を増やし、クロック速度を上げなくても並列で処理を行うことにより、処理能力を高めようとするものです。並列のビット数を増やして、クロック速度を低下させるメモリの「Wide IO」と同じ考えです。マルチコアでの並列処理で処理能力が向上させるために、OSやアプリケーションソフトもマルチコア対応になってきました。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 日本が再び世界をリードするための、“シン”モノづくりの世界

- 自動車工場で聞こえるのに、食品工場では聞こえない音〜工場の主人公は誰か

- 「自動車以外は全て好調」、四半期受注過去最高のDMG森精機が通期予想上方修正

- エンジニアリング業務を自律実行、シーメンスが産業AIを新たな段階に

- マグネットで触れるだけ、振動値を5秒で判定する回転機振動チェッカー

- 「ロボット大国」日本の逆襲、地道なモノづくりが世界を動かす交渉力に

- 猛暑に備えて

- 工場の主人公は誰なのかという問いかけ、元トヨタ生技が見た食品工場のなぜ

- なぜオムロンは農業の“作業”ではなく“判断”の自動化を目指すのか

- ヒューマノイド中核部品がハノーバーメッセ技術賞、“脱自動車”のシェフラー開発

コーナーリンク