第26回 TSV実用化に向けて:前田真一の最新実装技術あれこれ塾(4/4 ページ)

4. TSVの技術発表

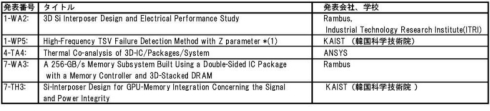

表1と表2、昨年(2012年)のDAC(Design Automation Conference)と今年のDesignConの発表でTSV、2.5D、3D実装に関連した技術発表をリスト化しました。

DACはIC設計のEDA(Electronic Design Automation)関連のコンベンションでLSIの設計、設計ツールの発表が主です。このため、大学からの発表も多く、アカデミックな論理的発表が多くなっています。

DesignConはDesign Conventionの意味で、システムICから基板までシステム設計に関する発表が主となっています。このためメーカーからの発表が多く、具体的な設計などの話題が多くなっています。

どちらの発表も近年は韓国や台湾などアジアからの発表が多くなっています。

残念ながら日本からの発表は大変少なく、特に大学の発表はほとんど見受けられません。

ここでも韓国や台湾のエレクトロニクス業界と日本の業界の勢いの差を感じます。また大学からの発表がなく、将来的な展望も気がかりです。

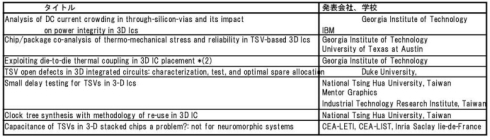

やはりDACの発表はTSVの解析モデル化や解析の手法などが多いですが、解析には電気特性と熱解析があります(図12)。

図12 TSVの熱対策(DAC、Exploiting die-to-die thermal coupling in 3D IC placement Georgia Institute of Technology)(クリックで拡大)

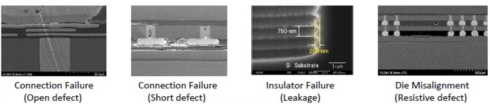

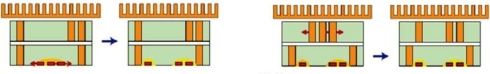

図12 TSVの熱対策(DAC、Exploiting die-to-die thermal coupling in 3D IC placement Georgia Institute of Technology)(クリックで拡大)DesignConではやはり熱解析モデルや電気解析モデルに関する発表もありますが、製造不良解析に対する発表もあります(図13)。

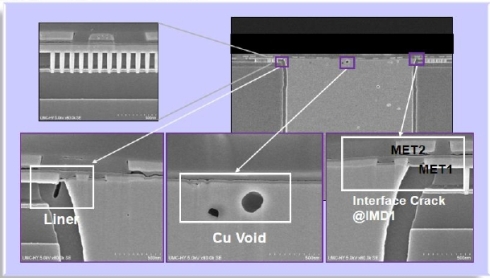

TSVの製造不良については、Hot Chips 24でのUMCの発表でも、開発初期ではいろいろなエラーが発生したものの、現在はこれらの問題は解決している、という発表もありました(図14)。

チップの3D実装に関しては、電気的な特性に関しては多くのメリットがありますが、熱は大きな問題となるといわれています。

このため、学会などでも今回紹介した以外にも多くの発表があります*2)。

*2)エレクトロニクス実装学会誌, 2013.Jan、Electronics Packaging 2012, 1, FEM Analysis on Mechnical Stress of 2.5D Packaging Interposers, Toshiya Hisada, Toyohiro Aoki, Junko Asai, Yasuharu Yamada IBM

2.5D実装にあたっては、シリコンインタポーザはガラスエポキシインタポーザよりも熱導電率が高く、チップ面積も1チップSoCよりも多少大きくなります。このため、チップスケールパッケージ(CSP)LSIよりも多少良くなるともいわれています。

また、現在、すでに実用化がされているメモリチップの3D実装についても熱の問題は大きくありません。

これは、メモリチップのスタッキングはメモリチップの容量を増やすために行われるものだからです。いくらメモリチップを重ねても動作モードが現在の8ビットや16ビットの並列動作では、動作する回路は指定されたアドレスだけで発熱量は増えないからです。逆に、3D実装によりドライバを微小電流で駆動できるようになり、消費電流が下がります。

しかし、CPUやSoCの積層や同時に512ビットのデータをアクセスするWide I/Oメモリの積層ではパッケージの消費電力が増加し、発熱や同時スイッチングノイズの問題が解決すべき問題として大きく立ちはだかってきます。

2.5D実装やメモリチップの3D実装でTSVの普及を図りつつ、2〜3年で課題を解決し、本格的なTSVを使った3D実装を立ち上げる流れが見えてきました。

日本は個々の技術はあるのですが、3D実装で何をしたいのか、何が変わるのか、トップマネジメントによるビジネスモデルが見えていないような感じがします。

iPhoneやiPadをAppleが大ヒットさせたときもそうでしたが、「何も新しい技術はない。こんなものはわが社でも簡単に作れる」というようなトップマネジメント丸出しの姿勢を打ち出すのではなく、ビジネスビジョンをもった開発を進めることを期待します。

筆者紹介

前田 真一(マエダ シンイチ)

KEI Systems、日本サーキット。日米で、高速システムの開発/解析コンサルティングを手掛ける。

近著:「現場の即戦力シリーズ 見てわかる高速回路のノイズ解析」(技術評論社)

関連記事

- ≫前田真一の最新実装技術あれこれ塾

第25回 量産技術化が進むTSV

第25回 量産技術化が進むTSV

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第25回は、量産技術として開発が加速しているTSV(Through Silicon Via)の最新動向を解説する。 第13回 TSVが量産技術へ〜Wide I/O規格

第13回 TSVが量産技術へ〜Wide I/O規格

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第13回は、JEDECが2011年末に規格内容を正式に発表した、次世代メモリインタフェース「Wide I/O」について説明する。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 軸受業界再編へNSKとNTNが経営統合に基本合意、両トップが語った危機感とは

- なぜオムロンは農業の“作業”ではなく“判断”の自動化を目指すのか

- 日本が再び世界をリードするための、“シン”モノづくりの世界

- 接触前に停止する協働ロボットに18kg可搬が登場、動作範囲も拡張

- オムロンの制御機器事業が「再成長」に転換、M&Aで欧米顧客基盤を強化へ

- 「自動車以外は全て好調」、四半期受注過去最高のDMG森精機が通期予想上方修正

- 成功率90%超でコンテナ搬送、ヒューマノイドをシーメンス工場に試験導入

- 最大26kWの超高出力化が可能、アマダが新たなファイバーレーザーマシン

- オムロンが電子部品事業を米国投資会社に売却、新会社名はAratasに

- ヒューマノイド導入を支援するコントローラー、既存手法とVLAモデルを統合

コーナーリンク