第25回 量産技術化が進むTSV:前田真一の最新実装技術あれこれ塾(1/4 ページ)

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第25回は、量産技術として開発が加速しているTSV(Through Silicon Via)の最新動向を解説する。

本連載は「エレクトロニクス実装技術」2013年4月号の記事を転載しています。

1. TSVの普及へ

最近、TSV(Through Silicon Via)への関心が特に高まっています。

実装に関連する学会や、コンベンション、セミナーなどでは、必ずといってよいほどTSV関連の発表、講演があります。

例えば、日本では今年(2013年)1月に開かれた「ネプコン ジャパン2013」では、「インターネプコンジャパン」と「半導体パッケージング技術展」での技術セミナーは3次元実装、TSVの話題が目白押しでした。

これはアメリカでも同じで、日本よりも積極的に、多くの発表がなされています。

昨年(2012年)夏のICのコンベンション「HotChips」では、TutorialとしてTSVの講演が組まれていましたし、パッケージのシンポジウム「IMAPS(International Symposium on Microelectronics)」や「DesignCon」、IEEEの「ECTC(IEEE Electronic Components and Technology Conference)」など、どのコンベンションでも必ずTSVの発表がいくつかはあります。

今後の技術動向として、半導体チップの3次元実装は必然的な流れとなっていることは誰もが認めるところです。

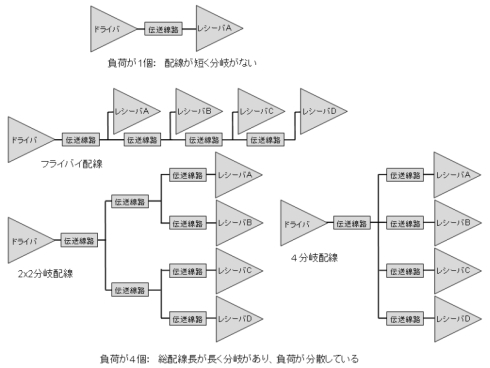

例えば、モバイル機器からサーバ、スーパーコンピュータまで、すべての機器で使用するメモリの量は急激に増えています。それに対して、メモリのチップ容量の増加はDDRでは回路は究極まで簡単化され、ICの微細化によるも増加だけです。チップ容量の増加は、要求の増加に比較して、遅々としたものです。しかも、データの転送速度の高速化のため、多くのチップをメモリバスに接続すると信号波形が乱れてしまい、接続できるメモリチップの数を増やすことは困難です(図1)。

メモリの容量を2倍、4倍と飛躍的に増加させる方法として、メモリチップを3次元実装が解決になります。

TSVを使ってメモリチップを3次元実装すれば、伝送線路的に見れば、メモリ間の接続は非常に短くなり、伝送路的には1つの負荷に見えるので、2個、4個と接続することができるはずです。

DDR4メモリや携帯機器用の新しいメモリであるWide I/Oメモリなどは、メモリのスタック実装が前提となった規格となっています。

シリアルデータ転送でも28Gbpsなどという高速伝送が現実となりつつあり、ここでは、銅か光かが競合しています。光伝送のためにはドライバのレーザICとレシーバのフォトICが必要となります。光伝送が銅に劣る点はこれらの光ICの価格とシステムの集積度です。

光ICとCMOSによる論理ICでは、その材料の構造が異なります。このように材質や構造がことなるICをヘテロジニアスICと呼び、研究が盛んに行われています。

しかし、残念ながらまだヘテロジニアスICは単一構造のモノジニアスICに比べ、コスト、集積度、性能で劣っているのが現状です。

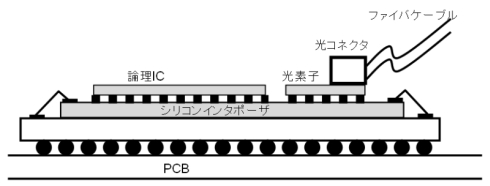

このヘテロジニアスICをモノジニアスで作成しようとして、シリコンインターポーザを使って2.5次元実装したMCMが作成されています(図2)。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 日本が再び世界をリードするための、“シン”モノづくりの世界

- 自動車工場で聞こえるのに、食品工場では聞こえない音〜工場の主人公は誰か

- 「自動車以外は全て好調」、四半期受注過去最高のDMG森精機が通期予想上方修正

- エンジニアリング業務を自律実行、シーメンスが産業AIを新たな段階に

- マグネットで触れるだけ、振動値を5秒で判定する回転機振動チェッカー

- 「ロボット大国」日本の逆襲、地道なモノづくりが世界を動かす交渉力に

- 猛暑に備えて

- 工場の主人公は誰なのかという問いかけ、元トヨタ生技が見た食品工場のなぜ

- ヒューマノイド中核部品がハノーバーメッセ技術賞、“脱自動車”のシェフラー開発

- 防衛事業の生産体制強化、ソナーなど水中音響センサーの新生産棟を建設

コーナーリンク