第25回 量産技術化が進むTSV:前田真一の最新実装技術あれこれ塾(2/4 ページ)

2. TSVの必要性

これまでもMCM-Dやメモリチップを積層して容量を増やした製品は存在しました。

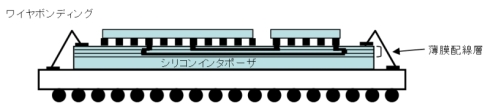

チップの積層はワイヤーボンディングを使って実現できます(図3)。

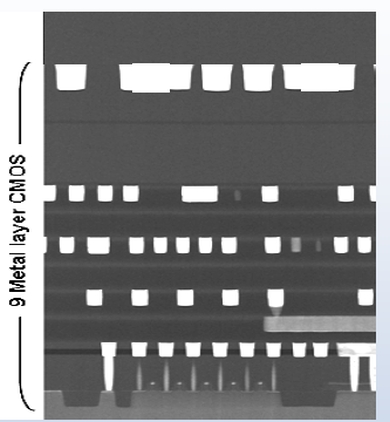

シリコンインタポーザの積層配線はIC内部の配線と同様に作成できます。現在、IC内部の配線層(メタル層)は10層以上となっています(図4)。

インタポーザにはこれほどの多層は必要ありません。シリコンインタポーザからパッケージのインタポーザへワイヤーボンディングで接続すれば簡単です(図5)。

TSVを使用するメリットは現在、SiP(System in Package)の集積度向上に注目されています。

例えば、ワイヤボンディングを使ったチップの3次元実装ではチップをずらせて積層する必要があります。また、チップにボンディングをする際にチップに力がかかるので、チップを薄くすることができず、積層すると厚くなります。さらに、ボンディングパッドの数が多くなり、パッドのエリアもインタポーザ上に広く必要となります(図6)。

しかし、TSVのメリットはこれだけではありません。電気特性の向上に大きな意味があります。

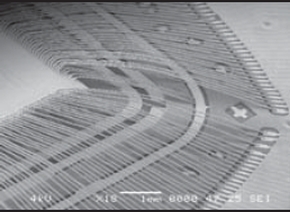

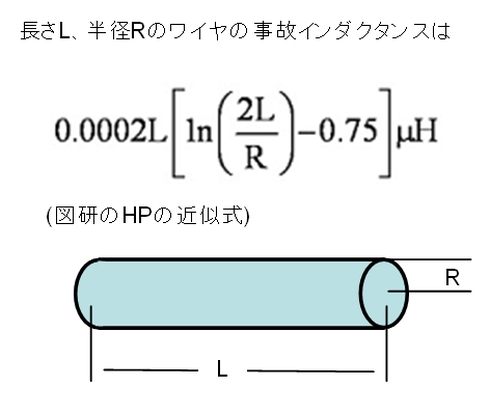

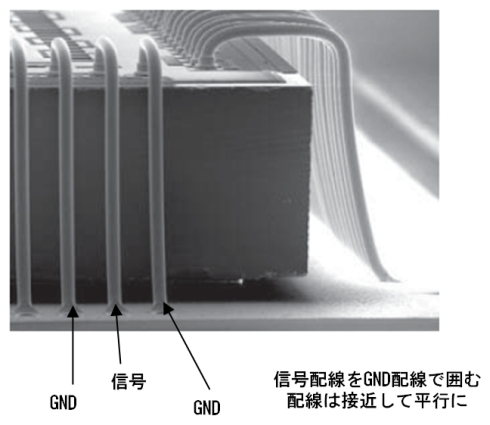

ボンディングパッドのピッチを狭くするためにはボンディングワイヤの径は細くする必要があります。また、パッドの数の増加に従い、チップとパッドとインタポーザのパッド距離が長いものが多くなります(図7)。

細くて長いワイヤは大きなL成分をもちます。

L成分は信号の伝搬を遅らせ、波形歪みの原因となります。

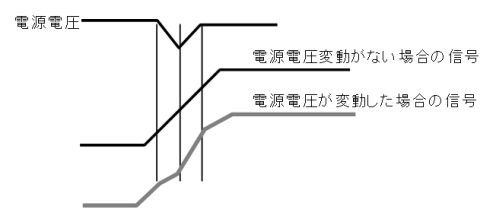

例えば、現在注目されている問題にPI(Power Integrity)があります。これは、ICの消費電力の変化によって、ICの電源電圧が変動し、信号のタイミングを変化させたり、電磁放射の原因となったりします(図8)。

この電源供給ラインに存在するL成分がICの電圧変動の原因となっています。

TSVを使用することにより、電源電圧変動(バウンス)を大幅に減少させることができます。

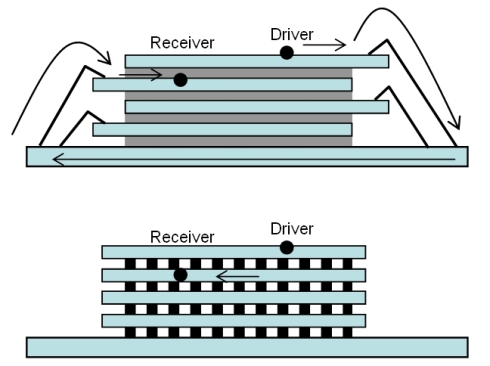

高速信号の伝送も同じです。例えば複数のメモリチップをコントローラの上に積層した場合、TSVを使用すれば、コントローラと各メモリチップは最短で結ばれ、少ない電流で歪みのないデータ伝送が実現できます(図9)。

しかし、同じ積層でもワイヤボンディング接続では、細くて長い配線を介し、各チップが結ばれます。しかもワイヤは伝送線路としてみても、インピーダンスの制御が困難です(図10)。長く不安定な伝送線路で信号を伝えるためには、電流を多く流し、終端で波形を整える必要があります。

大電力を使って、品質の悪い信号を伝達します。

例えば、韓国Hynix Semiconductor社はDDR3メモリチップを8層積層した場合、TSVではワイヤボンディングに比べ動作速度の50%向上、消費電を40%削減が達成できたと2011年3月に発表しました(図11)。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 「ロボット大国」日本の逆襲、地道なモノづくりが世界を動かす交渉力に

- 牧野フライスTOBに中止勧告、投資ファンド「大きな驚きをもって受け止め」

- 自動車工場で聞こえるのに、食品工場では聞こえない音〜工場の主人公は誰か

- 複雑化/大型化するダイカスト部品の高速外観検査、NTNが新たな事業の柱模索

- ヒューマノイド中核部品がハノーバーメッセ技術賞、“脱自動車”のシェフラー開発

- ニデックがプレス機の新工場開設、生産能力倍増で工作機械とのクロスセル推進

- ファナックが中央テクニカルセンタ建設、ロボットやFAの展示体験施設

- CT×AI×ロボットアームでリチウムイオン電池セルをインライン3D全数検査

- ロボット動作を直感的に記録/再生、プログラミング不要で教示可能に

- ブラザー工業がパレットチェンジャー搭載シリーズの新モデル、主軸性能強化

コーナーリンク

図3 ボンディングを使ったチップの積層(エルピーダメモリ

図3 ボンディングを使ったチップの積層(エルピーダメモリ  図4 ICの多層配線(9層)(Tier Logic Hot Chips 2010)

図4 ICの多層配線(9層)(Tier Logic Hot Chips 2010)

図6 大きなボンディングパッド領域が必要(SPT社資料より)

図6 大きなボンディングパッド領域が必要(SPT社資料より) 図7 細くて長い配線は大きなLをもつ

図7 細くて長い配線は大きなLをもつ 図8 電源電圧変動はノイズ源

図8 電源電圧変動はノイズ源

図11 Hynixの8層積層メモリ(Server Memory Forum 2012)

図11 Hynixの8層積層メモリ(Server Memory Forum 2012)