第25回 量産技術化が進むTSV:前田真一の最新実装技術あれこれ塾(4/4 ページ)

5. 逆転の発想

これまで、どちらかというと、TSVは、ICチップの積層による飛躍的な集積度向上を実現する技術として考えられてきました。これは、ICの微細化による集積度の向上が遅く、限界もいわれ始めている中モバイル機器などでは、処理速度の向上とメモリ容量の増大が強く要求されているからです。

特に日本では部品の小型化が得意分野でもあり、ICチップの積層により、ピン数も増えずに大狭量なCSP(Chip Size Package)ができれば、付加価値が上がり、TSVのコストを吸収できるのではないかと考えられてきた向きもあります。

信号の高速化や低消費電力でも同じです。TSVは高価なので、高性能化により、価格をカバーしようと考えていました。

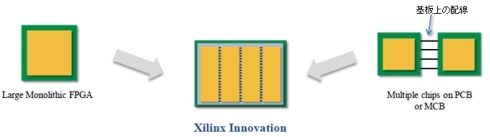

ところが、2010年にXilinx社がTSVを使った2.5次元のMCMを発表し、2011年に製品化しました。

Xilinx社の製品は大きな1チップで実現できる製品をあえて、小さな4チップに分割し、それらを困難な3次元実装をするのではなく、単にシリコンインタポーザの上に平面実装したものでした。

それまでの3次元実装と異なるTSVの応用で、これまでのMCMをTSVを使ったシリコンインタポーザで実現したもので、2.5次元実装と呼ばれるようになりました。

ここでの要点は大きな1チップでSoC(System on Chip)を作るより、小さな4チップに分割してTSVを使ったSiPにしたほうが安くできるというものでした(図19)。

それまでの常識を破って、既存実装技術で作るよりも、TSVの方が安くできるということで、各社の取り組みが変化しました。

6. Wide I/O規格

2011年の12月に各種規格を制定するJEDECから、まったく新しいモバイル機器用のメモリ規格として、Wide I/O規格が制定されました。

モバイル機器用メモリ規格とは、コンピュータ用のダイナミック・メモリの規格であるDDRメモリ規格(DDR、DDR2、DDR3、DDR4規格)の低消費電力版のメモリ規格です。

モバイル機器用のメモリには低消費電力のほかに機器の小型化が実現できるように要求されます。

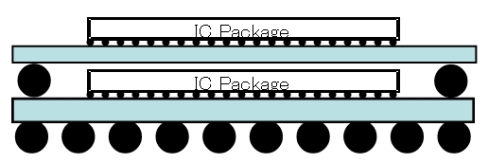

このため、これまでのモバイル用メモリ規格であるLPDDR規格やLPDDR2規格では一般的なコントローラICとメモリを基板上に実装する規格のほか、コントローラICの上にメモリICを実装するためのPoP(Package on Package)実装が規格化されていました(図20 )。

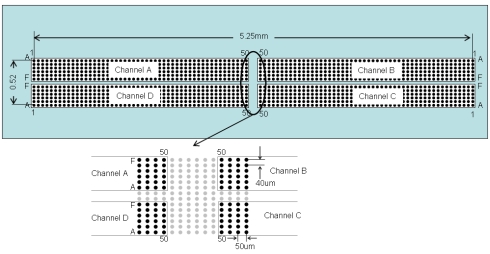

このWide I/Oメモリ規格では、PoP実装ではなく、コントローラチップの上に直接メモリチップを実装するチップの3D実装が規格化されています(図21)。

ただ、2012年時点では、コントローラチップとメモリチップをTSVを使って、3D実装をした製品をすぐに量産化することは困難だとは、全員が理解していました。

実際、この規格では、ほかのメモリ規格で定められている信号の電気特性については基本的なことしか決定していませんでした。

これは、パッドのピッチや形状、数など3次元実装するための機械的規格を定めて、コントローラやメモリの3次元実装への開発をしやすくし、開発をスピードアップする目的が大きい規格です。

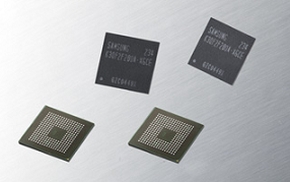

実際、モバイル用メモリとしては、Wide I/O規格より遅れて、昨年(2012年)5月に規格が規定された、LPDDR3規格のメモリは昨年9月から、すでに製品化されています(図22)。

LPDDR3規格はLPDDR2規格と同じ、PoP実装か基板上の平面実装を使った、LPDDR2規格の高速版です。

一方、Wide I/O規格が定まった昨年は3D実装の熱検討などや、信号試験などTSVの製品化へ向けての発表が、Wide I/O規格でのパッドレイアウトで多く発表されるようになりました。

また、2015年には本格的なWide I/Oメモリ規格としてWide I/O 2規格が発表されるといわれています。

現在のWide I/O規格は、クロックの周波数に対してデータの最大周波数は半分となる、SDR(Single Data Rate)の規格です。当然、同じようにロック周波数に対して、SDRはDDRに比べて半分のデータ転送速度にしかなりません。これがWide I/O規格では現在一般に使われているDDR(Double Data Rate)規格になります。本格的な製品版規格のWide I/O 2規格です。

JEDECの規格スケジュールを見ても2015年というのがやはりTSVを使った3D実装の製品化が現実味を帯びてきます。

TSVを使った3D実装実用化までに、これからの1年しかないことになります。このため、最近の発表は実用化を見据えたものが多くなっています。

本連載で今後、そのいくつかを紹介します。

筆者紹介

前田 真一(マエダ シンイチ)

KEI Systems、日本サーキット。日米で、高速システムの開発/解析コンサルティングを手掛ける。

近著:「現場の即戦力シリーズ 見てわかる高速回路のノイズ解析」(技術評論社)

関連記事

- ≫前田真一の最新実装技術あれこれ塾

第13回 TSVが量産技術へ〜Wide I/O規格

第13回 TSVが量産技術へ〜Wide I/O規格

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第13回は、JEDECが2011年末に規格内容を正式に発表した、次世代メモリインタフェース「Wide I/O」について説明する。 第9回 TSVを前提としたモバイルDDR

第9回 TSVを前提としたモバイルDDR

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第9回は、モバイルDDRメモリの最新規格である、LPDDR3と、第3回で取り上げたTSVによって実現可能になったWide IOについて解説します。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 日本が再び世界をリードするための、“シン”モノづくりの世界

- 自動車工場で聞こえるのに、食品工場では聞こえない音〜工場の主人公は誰か

- 「自動車以外は全て好調」、四半期受注過去最高のDMG森精機が通期予想上方修正

- エンジニアリング業務を自律実行、シーメンスが産業AIを新たな段階に

- マグネットで触れるだけ、振動値を5秒で判定する回転機振動チェッカー

- 「ロボット大国」日本の逆襲、地道なモノづくりが世界を動かす交渉力に

- 猛暑に備えて

- 工場の主人公は誰なのかという問いかけ、元トヨタ生技が見た食品工場のなぜ

- ヒューマノイド中核部品がハノーバーメッセ技術賞、“脱自動車”のシェフラー開発

- 防衛事業の生産体制強化、ソナーなど水中音響センサーの新生産棟を建設

コーナーリンク

図20 PoP(Package on Package)実装

図20 PoP(Package on Package)実装

図22 LPDDR3メモリ(Samsung社

図22 LPDDR3メモリ(Samsung社