FPGAソフトコアCPUにおける最適化を検証する:MAX 10 FPGAで学ぶFPGA開発入門(14)(5/7 ページ)

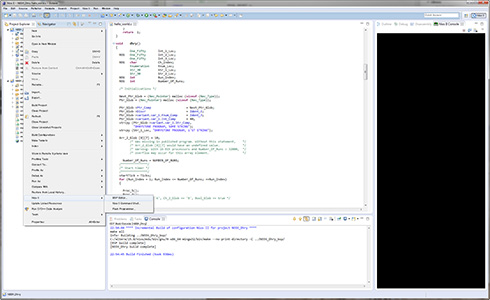

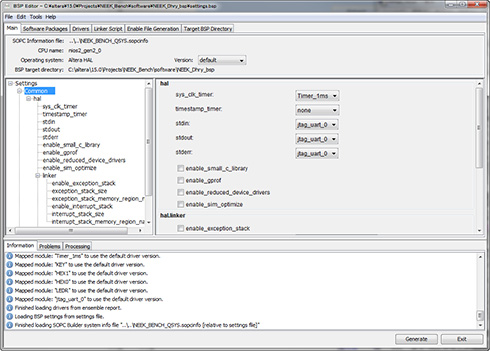

さてプログラムの説明はこのあたりにして、ビルドして動かしてみたい。ビルドのためにはまずdhry.hをプロジェクトに追加(Photo05)し、さらにEclipseからBSP Editorを呼び出して(Photo06)、sys_clk_timerにTimer_1msが指定されている事を確認しておく(Photo07)。このあたりの話は以前こちらで説明した通りだ。

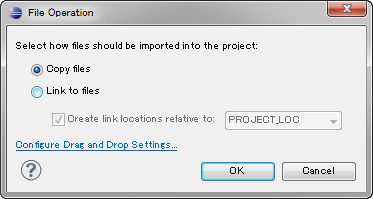

Photo05:dhry.hをドラッグ&ドロップでEclipseのNEEK_Dhryにコピーするとこのダイアログが出てくるので、"Copy files"を選ぶとプロジェクトフォルダにコピーされ、プロジェクトにも追加される

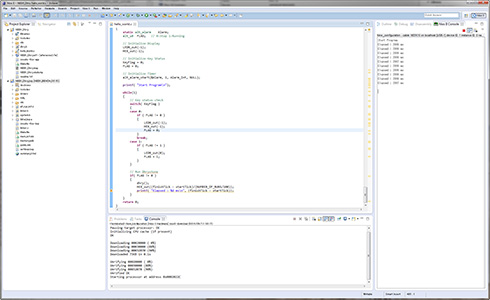

Photo05:dhry.hをドラッグ&ドロップでEclipseのNEEK_Dhryにコピーするとこのダイアログが出てくるので、"Copy files"を選ぶとプロジェクトフォルダにコピーされ、プロジェクトにも追加されるさて、ここまで完了したらビルドして実行する。ちなみにNUMBER_OF_RUNSにリスト通りの数値(100万)を指定すると30分以上帰ってこないので、まずデバッグがてらこれを10000に書き換えて実行してみる。結果はPhoto08の様に、1万回で2006〜2007msという結果になった。

前にも書いた通り、VAX 11/780の数字が1757.0 Dhrystone/secで、今回はおおむね4982.6 Dhrystone/secだから2.84 DMIPSという計算になる。MAX10 Evaluation Boardで試した時には3.34 DMIPSという数値だったが、今回は1ms毎に(Alarm_Int()内で)IORD_ALTERA_AVALON_PIO_DATA()を呼び出してキー押下を確認しているので、このオーバーヘッドの分遅くなったと思えば、まぁ納得できる数字である。

NIOS IIにおける最適化の効果

さて今回の本題はここから。以前こちらで紹介したが、NIOS IIを使う場合、OptimizingをOffにする事が推奨というか指示されている。理由は“compiler optimization may cause some problems while running the program”ということであるが、これをOffにしていたらそれは性能が出ないのも当然である(Photo09)。

ではこれをOnにするとどうなるか?

関連記事

FPGAの内蔵温度センサーから値を得る

FPGAの内蔵温度センサーから値を得る

アルテラのFPGA「MAX 10」には温度センサーが内蔵されており、自身の温度を測定可能だ。メガファンクション「ALTPLL」を使い、内蔵センサーからの値を得るまでを試みる。 オンボードされた温湿度センサーからFPGAで値を得る

オンボードされた温湿度センサーからFPGAで値を得る

FPGA「MAX 10」搭載開発ボード「MAX 10 NEEK」には各周辺機器が備えられており、そこにはTI製の温湿度センサーも含まれる。サンプルプログラムを元に、オンボードされたデバイスの制御を試みる。 「MAX 10 NEEK」でストップウォッチを開発し、内蔵メモリから起動する

「MAX 10 NEEK」でストップウォッチを開発し、内蔵メモリから起動する

アルテラのFPGA「MAX 10」を搭載した開発ボード「MAX 10 NEEK」にはLEDやフラッシュメモリなどの各周辺機器が備えられている。今回はLEDを使ったストップウォッチを開発し、内蔵メモリから起動する。 「MAX 10 NEEK」に搭載されたDDR3メモリを使う

「MAX 10 NEEK」に搭載されたDDR3メモリを使う

MAX10搭載開発ボード「MAX 10 NEEK」には各周辺機器が備えられており、その中にはDDR3メモリも含まれる。ソフトコアCPU「Nios II」からの利用も含めて手順を紹介する。 「MAX 10 NEEK」へソフトコアCPUを組み込む

「MAX 10 NEEK」へソフトコアCPUを組み込む

周辺機器の充実したMAX10搭載開発ボード「MAX 10 NEEK」に、ソフトコアCPU「NIOS II」を組み込み、ソフトコアCPUからボード搭載LEDの制御までを紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- 40台超のロボットを統合管理する自律運用システムが本格稼働

コーナーリンク