FPGAのソフトコアCPUをベンチマークで測定する:MAX 10 FPGAで学ぶFPGA開発入門(7)(5/6 ページ)

ソフトウェアを対応させる

次はソフトウェア側の対応である。ここでは追加した「sys_clk_timer」をシステムタイマーとして利用する事を教えてやらなければいけない。

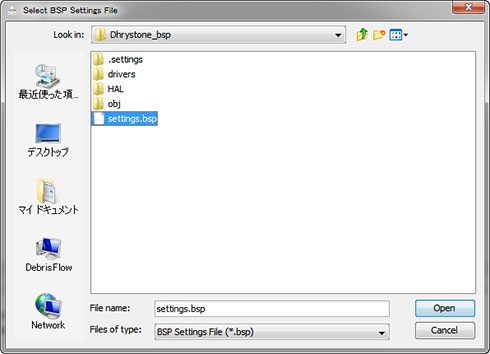

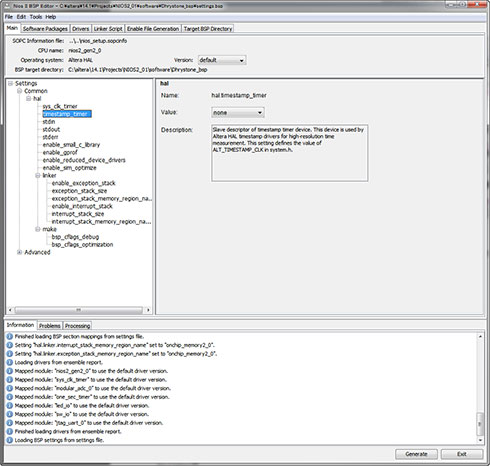

Eclipseの画面で「NIOS II」→「BSP Editor」を呼び出し(Photo08)、「Dhrystone_bsp」の下にあるsettings.bspを読み込むと、「timestamp_timer」の値が「none」になっているはずなので(Photo09)、これを「sys_clk_timer」とする。これが終わったら右下のGenerateボタンを押してBSPを生成し直す。

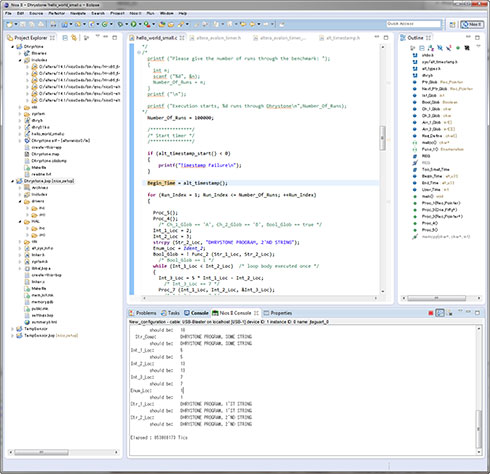

次にこれをプロジェクトに反映する。EclipseでBSP側を右クリックし、「NIOS II」→「Generate BSP」を選択した後にビルドしなおすと、今度はシステムクロックがちゃんと存在する状態でプログラムが構築される。そこで実行するとPhoto12の様に、キチンと所要時間が表示されるようになった。

さて、この所要時間は、実際にはTics(何Clock経過したか)なので、実際には50MHz駆動で8億5300万173clockということで、17.06秒ほどの時間となる。10万回で17.06秒なので性能は大体5861.7 Dhrystone/secという数値になる。基準となるVAX11/780のスコア(1757.0 Dhrystone/sec)と比較すると3.34 DMIPSという計算である。

これが速いか遅いかはどう使うか次第ではあるが、こちらのページに記載されている値に比べると、MAXQよりやや遅い程度でTexas InstrumentsのMSP430F149よりは高速、というのはそう悪くないのではと思う。

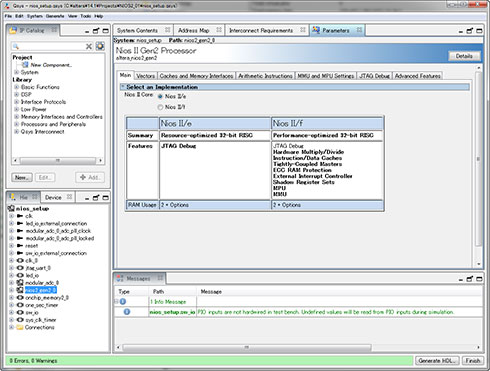

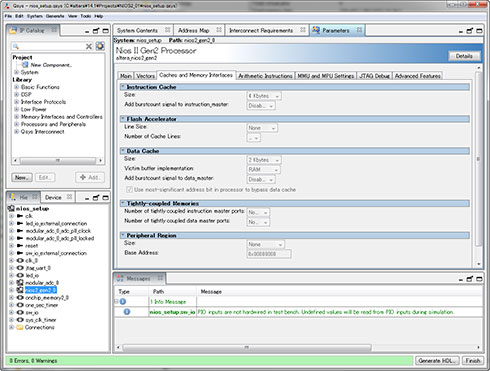

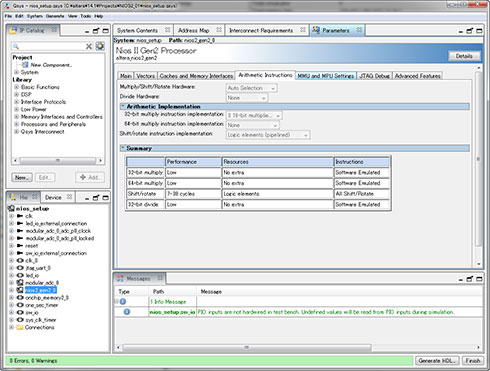

ちなみにQSYSでプロセッサの設定を見ていただく(Photo13〜15)と分かるのだが、今回はリソース最適化でプロセッサを構成しているので、このあたりを変更すればもっと性能は上がる可能性がある。興味のある方はぜひ、いろいろと設定を変えてみていただきたい。

ということでプロセッサが実用に耐えることが分かったので、次はもう少しデバイスと組み合わせてみたい。

関連記事

FPGA上でソフトコアCPUを動かす手引き

FPGA上でソフトコアCPUを動かす手引き

これまでFPGAの開発基礎としてLチカなどを紹介してきたが、今回はちょっと目先を変えてFPGA上でのCPUコア動作に取り組む。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 よろしいならばダイナミック点灯だ――FPGAでLEDをダイナミックにLチカさせる

よろしいならばダイナミック点灯だ――FPGAでLEDをダイナミックにLチカさせる

単純なLチカならばFPGAでもそう難しくない。ただ、ダイナミック点灯やそれに伴うソースの最適化については“ならでは”のポイントが散見される。今回も連載で利用している「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 FPGAのLED制御プログラムを深く理解する

FPGAのLED制御プログラムを深く理解する

FPGA開発に必要なHDLへの理解を深めるため、MAX 10に用意されているArduino I/Oを利用してのLチカを行い、多灯LEDの制御を含めたプログラミングも解説する。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 FPGAでのLチカをVerilog HDLで理解する

FPGAでのLチカをVerilog HDLで理解する

今回はFPGAでのLチカを例に、FPGA開発に必要なハードウェア記述言語の解説をしたい。用いる「Verilog HDL」はArduinoやCの経験がある方なら、理解そのものはそう難しくないと思う。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 「MAX 10 FPGA」のテスト環境を構築する

「MAX 10 FPGA」のテスト環境を構築する

今回から実際に「MAX 10 FPGA評価キット」を利用しての開発に着手する。まずは環境構築だ。キット以外に必要なモノもあるので注意して欲しい。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 なぜFPGAが注目されるのか、開発ボードに触れて確認する

なぜFPGAが注目されるのか、開発ボードに触れて確認する

最近では「FPGAの重要性」について語られる機会が増え、適用事例も増加している。ではなぜ今FPGAなのか。実際の開発ボードでFPGAを学びながら、FPGAへの理解を深めよう。連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントもご用意。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 4年目を迎えた「小さく始めるAIパビリオン」、マイコンよりMPU多めの構成に

コーナーリンク