FPGA僜僼僩僐傾CPU偵偍偗傞嵟揔壔傪専徹偡傞丗MAX 10 FPGA偱妛傇FPGA奐敪擖栧乮14乯乮1/7 儁乕僕乯

MAX10搵嵹奐敪儃乕僪乽MAX 10 NEEK乿偱僜僼僩僐傾CPU乽NIOS II乿傪棙梡偡傞嵺丄嵟揔壔偟側偄偙偲傪悇彠偝傟傞偑丄愝掕帺懱偼巤偣傞丅偱偼嵟揔壔偡傞偲懍偔側傞偺偐丠桳彏斉傕娷傔偰専徹偡傞丅

丂傾儖僥儔偺FPGA乽MAX 10乿傪梡偄偨奐敪庤朄傪徯夘偟偰偄傞偙偺楢嵹傕丄崱夞偱偄偭偨傫偺廔椆偲側傞丅MAX 10 NEEK傪庤偵擖傟偰偐傜丄FPGA偲偄偆傛傝偼僜僼僩僐傾CPU偱偁傞乽NIOS II乿偵僞乕僎僢僩偑僔僼僩偟偨姶傕偁傞偺偩偑丄嵟廔夞傕堷偒懕偒NIOS II偺惈擻傪傕偆偪傚偭偲捛偄偐偗偰傒偨偄偲巚偆丅

丂埲慜偵傕怗傟偨偑丄NIOS II傪巊偆応崌偵偼嵟揔壔傪峴傢側偄傛偆巜帵偝傟偰偄傞丅僾儘僌儔儉幚峴偵栤戣偺惗偠傞壜擻惈偑偁傞偨傔偲偝傟偰偄傞偑丄嵟揔壔偟側偗傟偽惈擻偑弌側偄偺傕傑偨摉慠偱偁傞丅偦偙偱丄儀儞僠儅乕僋僾儘僌儔儉傪梡堄偟偰嵟揔壔偺岠壥傪専徹偟偨偄丅

System Builder偱偺娐嫬峔抸

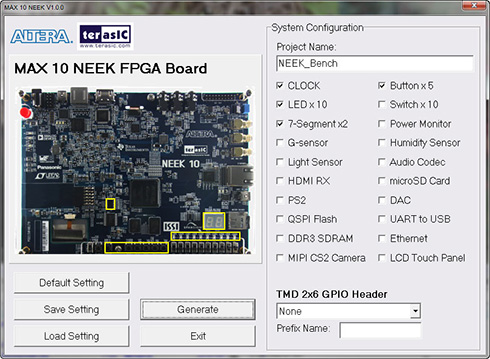

丂傑偢偼偍側偠傒偺System Builder乮Photo01乯偱僥儞僾儗乕僩傪嶌傞丅崱夞偼乮偁傑傝巊偆堄枴偼側偄偺偩偑乯7僙僌儊儞僩LED偲10屄偺LED丄僾僢僔儏儃僞儞乮偲Clock乯傪桳岠偵偟偨丅僾儘僕僃僋僩柤偼乽NEEK_Bench乿偲偟偨偺偱丄CodeGenerate/MAX10/ 偺壓偵乽NEEK_Bench乿偲偄偆僼僅儖僟偑惗惉偝傟傞丅偙傟傪娵偛偲Quartus II偺僾儘僕僃僋僩僨傿儗僋僩偵僐僺乕偡傞丅

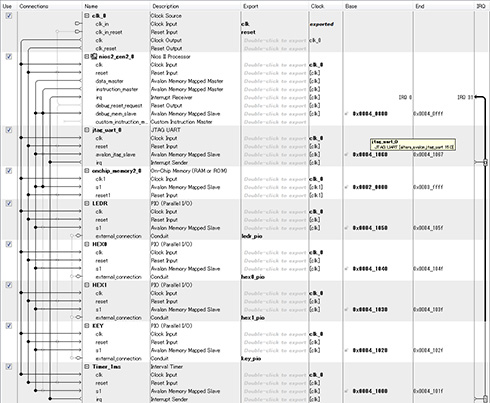

丂師偵Quartus II乮15.0傪棙梡乯傪婲摦偟偰丄乬File乭 仺 乬Open Project...乭偱乬NEEK_Bench.qpf乭傪慖戰偡傞丅弶婜忬懺偱偼NEEK_Bench.v偺拞偵偼NEEK_Bench偲偄偆儌僕儏乕儖掕媊偑峴傢傟偰偄傞偩偗側偺偱丄偙偙偐傜qsys傪摦偐偟偰丄僐儞億乕僱儞僩傪捛壛偡傞丅捛壛偡傞偺偼僾儘僙僢僒僐傾丄JTAG UART丄僆儞僠僢僾儊儌儕丄LEDR丄HEX0丄HEX1丄KEY丄僞僀儅乕偺8偮偩丅

| 僐儞億乕僱儞僩 | 捛壛曽朄 |

|---|---|

| 僾儘僙僢僒僐傾 | "Processors and Peripherals" 仺 "Embedded Processors" 仺 "NIOS II Processor"偱捛壛丅庬暿偼NIOS II/e傪巜掕 |

| JTAG UART | "Interface Protocols" 仺 "Serial" 仺 "JTAG UART" |

| 僆儞僠僢僾儊儌儕 | "Basic Functions" 仺 "On Chip Memory" 仺 "On-Chip Memory 乮RAM or ROM乯"丅儊儌儕梕検偼128KB偲偟丄"Initialize memory content"偺僠僃僢僋傪奜偟偰偍偔丅傑偨偙傟傪捛壛屻偵丄nios2_gen2_0偺僾儘僷僥傿傪奐偒丄"Vectors"僞僽偱"Reset Vector"偲"Exception Vector"傪嫟偵"onchip_memory2_0.s1"偵愝掕偡傞丅 |

| LEDR乮LED亊10乯 | "Processors and Peripherals" 仺 "Peripherals" 仺 "PIO乮Parallel I/O乯"偱PIO傪捛壛偡傞丅偙偺嵺Width傪10bit丄Direction偼Output傪巜掕偟乮Photo02乯丄柤慜傪"LEDR"偵曄峏偡傞丅傑偨Conduit傪"ledr_pio"偲偡傞丅 |

| HEX0乮7僙僌儊儞僩LED #1乯 | "Processors and Peripherals" 仺 "Peripherals" 仺 "PIO乮Parallel I/O乯"偱PIO傪捛壛偡傞丅偙偺嵺Width傪7bit丄Direction偼Output傪巜掕偟丄柤慜傪"HEX0"偵曄峏偡傞丅傑偨Conduit傪"hex0_pio"偲偡傞丅 |

| HEX1乮7僙僌儊儞僩LED #2乯 | "Processors and Peripherals" 仺 "Peripherals" 仺 "PIO乮Parallel I/O乯"偱PIO傪捛壛偡傞丅偙偺嵺Width傪7bit丄Direction偼Output傪巜掕偟丄柤慜傪"HEX1"偵曄峏偡傞丅傑偨Conduit傪"hex1_pio"偲偡傞丅 |

| KEY乮Button亊5乯 | "Processors and Peripherals" 仺 "Peripherals" 仺 "PIO乮Parallel I/O乯"偱PIO傪捛壛偡傞丅偙偺嵺Width傪5bit丄Direction偼Input傪巜掕偟丄柤慜傪"KEY"偵曄峏偡傞丅傑偨Conduit傪"key_pio"偲偡傞丅 |

| 僞僀儅乕 | "Processors and Peripherals" 仺 "Peripherals" 仺 "Interval Timer"偱捛壛丅Period偼1ms傪巜掕丅Counter Size偼32bit偺傑傑偲偡偟丄柤慜傪"Timer_1ms"偲偡傞丅 |

丂捛壛屻偵奺僐儞億乕僱儞僩偺寢慄傪峴偄乮Photo02乯丄偝傜偵Qsys偺乬System乭 仺 乬Assign Base Address乭偱傾僪儗僗偺妱傝摉偰捈偟傪峴偆丅偙傟偱婎杮揑偵Qsys偺僄儔乕偑徚偊傞偼偢側偺偱丄乬NEEK_BENCH_QSYS乭偲偄偆柤慜傪偮偗偰曐懚偟偨忋偱丄乬Generate HDL乭傪墴偟偰qip僼傽僀儖傪惗惉偟Qsys懁偺嶌嬈偼廔椆偱偁傞丅

丂偮偄偱NEEK_Bench.v偺曇廤偱偁傞丅偙偪傜傕廬棃偲偁傑傝曄傢傜偢丄嵟廔揑偵List 1偺條偵丄乽NEEK_BENCH_QSYS乿偲偄偆儌僕儏乕儖傪屇傃弌偡愝掕偩偗傪捛壛偡傟偽姰椆偱偁傞丅

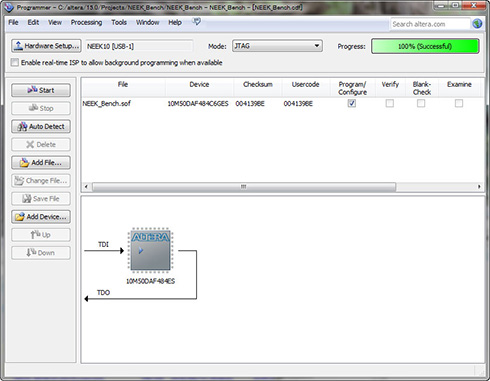

丂偙傟偑廔傢偭偨傜僐儞僷僀儖偟丄僄儔乕偑側偗傟偽Programmer偱NEEK_Bench.sof傪彂偒崬傫偱Quartus II懁偺嶌嬈偼廔椆偱偁傞乮Photo03乯丅

娭楢婰帠

FPGA偺撪憼壏搙僙儞僒乕偐傜抣傪摼傞

FPGA偺撪憼壏搙僙儞僒乕偐傜抣傪摼傞

傾儖僥儔偺FPGA乽MAX 10乿偵偼壏搙僙儞僒乕偑撪憼偝傟偰偍傝丄帺恎偺壏搙傪應掕壜擻偩丅儊僈僼傽儞僋僔儑儞乽ALTPLL乿傪巊偄丄撪憼僙儞僒乕偐傜偺抣傪摼傞傑偱傪帋傒傞丅 僆儞儃乕僪偝傟偨壏幖搙僙儞僒乕偐傜FPGA偱抣傪摼傞

僆儞儃乕僪偝傟偨壏幖搙僙儞僒乕偐傜FPGA偱抣傪摼傞

FPGA乽MAX 10乿搵嵹奐敪儃乕僪乽MAX 10 NEEK乿偵偼奺廃曈婡婍偑旛偊傜傟偰偍傝丄偦偙偵偼TI惢偺壏幖搙僙儞僒乕傕娷傑傟傞丅僒儞僾儖僾儘僌儔儉傪尦偵丄僆儞儃乕僪偝傟偨僨僶僀僗偺惂屼傪帋傒傞丅 乽MAX 10 NEEK乿偱僗僩僢僾僂僅僢僠傪奐敪偟丄撪憼儊儌儕偐傜婲摦偡傞

乽MAX 10 NEEK乿偱僗僩僢僾僂僅僢僠傪奐敪偟丄撪憼儊儌儕偐傜婲摦偡傞

傾儖僥儔偺FPGA乽MAX 10乿傪搵嵹偟偨奐敪儃乕僪乽MAX 10 NEEK乿偵偼LED傗僼儔僢僔儏儊儌儕側偳偺奺廃曈婡婍偑旛偊傜傟偰偄傞丅崱夞偼LED傪巊偭偨僗僩僢僾僂僅僢僠傪奐敪偟丄撪憼儊儌儕偐傜婲摦偡傞丅 乽MAX 10 NEEK乿偵搵嵹偝傟偨DDR3儊儌儕傪巊偆

乽MAX 10 NEEK乿偵搵嵹偝傟偨DDR3儊儌儕傪巊偆

MAX10搵嵹奐敪儃乕僪乽MAX 10 NEEK乿偵偼奺廃曈婡婍偑旛偊傜傟偰偍傝丄偦偺拞偵偼DDR3儊儌儕傕娷傑傟傞丅僜僼僩僐傾CPU乽Nios II乿偐傜偺棙梡傕娷傔偰庤弴傪徯夘偡傞丅 乽MAX 10 NEEK乿傊僜僼僩僐傾CPU傪慻傒崬傓

乽MAX 10 NEEK乿傊僜僼僩僐傾CPU傪慻傒崬傓

廃曈婡婍偺廩幚偟偨MAX10搵嵹奐敪儃乕僪乽MAX 10 NEEK乿偵丄僜僼僩僐傾CPU乽NIOS II乿傪慻傒崬傒丄僜僼僩僐傾CPU偐傜儃乕僪搵嵹LED偺惂屼傑偱傪徯夘偡傞丅

Copyright © ITmedia, Inc. All Rights Reserved.

慻傒崬傒奐敪偺婰帠儔儞僉儞僌

- AMD偺PLD帠嬈傪攦廂偟堄婥尙崅偺Lattice Semiconductor偑FPGA嶲擖偱奟偭傉偪偵

- 旕岞奐壔偐傜巒傑傞乽晉巑僜僼僩 Gen.2乿丄AI亊IT亊OT偺梈崌偑彑偪嬝偵

- 嬻慜偺AI僽乕儉両乽擫傕庅巕傕AI乿側尰忬偼崱屻傕懕偔偺偐丠亂慜曇亃

- AI偑壓敿恎偺摦偒傪僒億乕僩丂娯崙敪偺僂僃傾儔僽儖儘儃僢僩乽WIM S乿偑擔杮偵忋棨

- 枩攷傪廔偊偨傾儞僪儘僀僪偨偪偺乽怴偨側廧傑偄乿丂挿扟岺偑昤偔恖偲媄弍偺岎嵎揰

- 擔棫偲擔棫僴僀僥僋偑撈帺僄僢僕AI敿摫懱傪奐敪丄愭抂GPU斾偱張棟岠棪10攞埲忋

- 徚旓揹棳20nA偲1.2V嬱摦傪椉棫偟偨帴婥僗僀僢僠梡AMR僙儞僒乕

- 僷儚乕僨僶僀僗偺懝幐傗壏搙忋徃傪悢昩偱専徹偱偒傞崅懍僔儈儏儗乕僞乕傪岞奐

- 暋悢偺FPGA僼傽儈儕乕偺惢昳儔僀僼僒僀僋儖僒億乕僩傪2045擭傑偱墑挿

- 40戜挻偺儘儃僢僩傪摑崌娗棟偡傞帺棩塣梡僔僗僥儉偑杮奿壱摥

僐乕僫乕儕儞僋