第40回 IBIS AMI:前田真一の最新実装技術あれこれ塾(1/4 ページ)

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第40回はIBIS AMIについて解説する。

本連載は「エレクトロニクス実装技術」2014年7月号の記事を転載しています。

1.損失対策

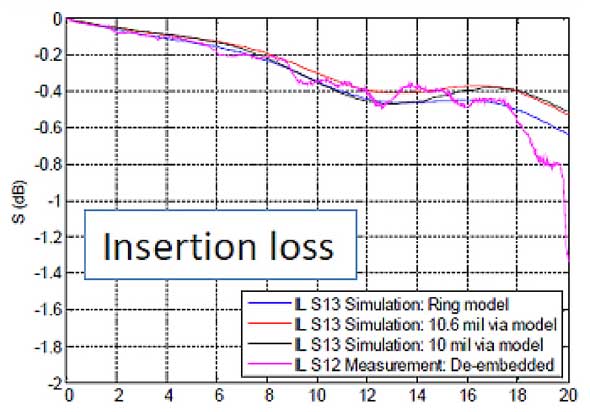

信号が高速になると、伝送線路での損失が大きくなります。損失は信号が高速になればなるほど大きくなります(図1)。

このため信号が高速化すると同時に、年々、損失の問題が大きくなってきています。損失は、誘電体材料の選択や、銅箔表面の平滑度を上げることにより、削減することはできますが、ゼロにすることはできません。

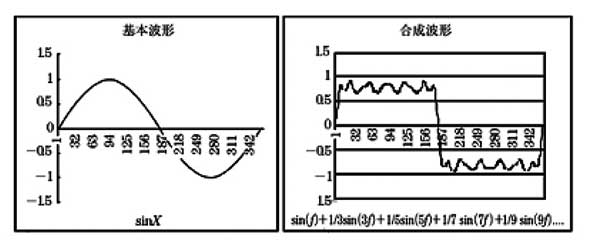

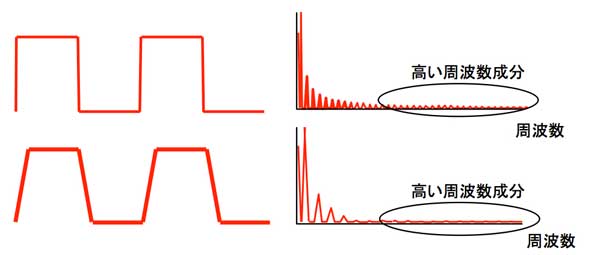

デジタル信号で使う方形波は多くの正弦波の合成波形です(図2)。

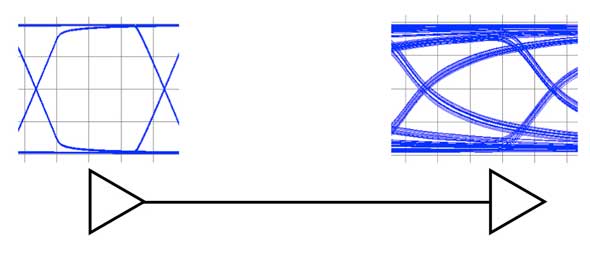

損失は周波数の高い寝具ほど大きくなるため、方形波の高い周波数成分になるほど大きな損失を受け、損失の影響で方形波がひずんできます(図3)。

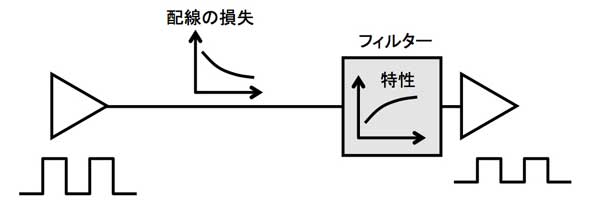

損失の影響を打ち消すためには、途中で高い周波数の信号ほど増幅するような増幅器(アンプ)を入れて、損失の影響を打ち消してやればよいことになります。または、損失の影響を見込んで、あらかじめ大きな信号を出力して途中で低い信号成分だけの振幅を減衰させるハイパスフィルターを挿入してやれば、受信端での信号は正しい方形波となります(図4)。

図5は10Gbpsの高速信号を伝送するケーブルのコネクタ部です。

コネクタの内部に高い周波数信号ほど増幅度が大きな増幅回路が組み込まれています。

損失は配線の長さに比例して大きくなるため、ケーブルの長さに応じて増幅度が変更されています。また、PCI ExpressやUSB 3.0など高速シリアル伝送方式の規格でも、このような損失対策として、損失を補うフィルタや高周波成分の出力を大きくする手法を盛り込んでいます。

例えば、PCI ExpressのGen1 (2.5GT/s)やGen2 (5.0 GT/s)(注1)ではデエンファシス(De-emphasis)と呼ばれる機能が規格化されています。

なお、USB 3.0はハードウェアの規格はPCI Express Gen2と全く同じものです。

逆に、PCI並列バスとPCI Expressはハード的には並列バスと直列データ転送で全く異なりますが、ソフトウェア的には互換性があり、同じドライバソフトが使えるようになっています。

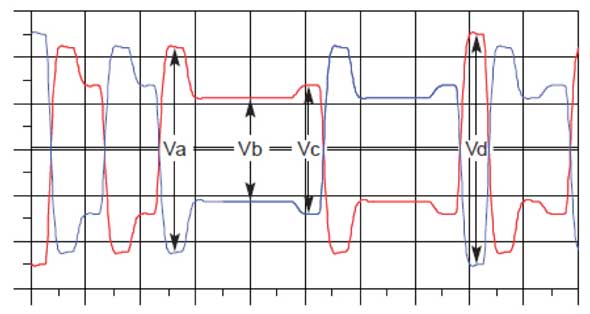

デエンファシスはドライバ側で、信号出力の特性を変化させて、損失の影響を補正するものです。

信号がハイからロー、ローからハイへと変化する時には信号振幅を大きくして、立ち上り/立ち下りの時間を早くします。これは信号の高い周波数成分がそのような性質を持つからです(図6)。

損失により信号の高い周波数成分が減衰して立ち上り/立ち下りが遅くなるのを補正するため信号振幅を大きくします。

それに対し、ハイやローが連続して信号の場合、信号に高い周波数成分が含まれないため、電力消費を少なくするため、信号振幅を小さくします(図7)。

信号を小さくするのでデエンファシス(de-emphasis)と呼ばれます。また、ドライバ側であらかじめデータ出力時に、減衰の効果を見込んだ処理をしているため、プリエンファシス (Pre-emphasis) とも呼ばれます。

信号速度が2.5 GT/sのGen1ではエンファシスの大きさは−3.5dbですが、さらに高速なGne2(5.0GT/s)では損失が大きくなるため、Gen1と同じ−3.0dbに加え、−6.0dbの設定も用意されています。

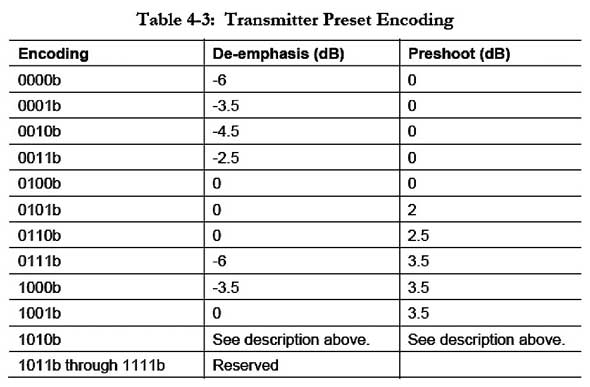

さらに高速なGen3(8GT/s)になると、ドライバの特性を −3.5db、−6.0db、に加え、−2.5db、−4.5dbときめ細かく設定できるようにすると同時に、レシーバ側にもフィルタを挿入し、ドライバとレシーバの特性の組み合わせで、損失による信号のひずみを補正できるようにしています(表1)。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 日本が再び世界をリードするための、“シン”モノづくりの世界

- 自動車工場で聞こえるのに、食品工場では聞こえない音〜工場の主人公は誰か

- 「自動車以外は全て好調」、四半期受注過去最高のDMG森精機が通期予想上方修正

- エンジニアリング業務を自律実行、シーメンスが産業AIを新たな段階に

- マグネットで触れるだけ、振動値を5秒で判定する回転機振動チェッカー

- 「ロボット大国」日本の逆襲、地道なモノづくりが世界を動かす交渉力に

- 猛暑に備えて

- 工場の主人公は誰なのかという問いかけ、元トヨタ生技が見た食品工場のなぜ

- ヒューマノイド中核部品がハノーバーメッセ技術賞、“脱自動車”のシェフラー開発

- 防衛事業の生産体制強化、ソナーなど水中音響センサーの新生産棟を建設

コーナーリンク

図1:損失は周波数が高いほど大きい

図1:損失は周波数が高いほど大きい 図2:方形波は多くの正弦波の合成波形

図2:方形波は多くの正弦波の合成波形 図3:損失により、方形波がひずむ

図3:損失により、方形波がひずむ 図4:損失を補正するフィルター

図4:損失を補正するフィルター 図5:コネクタ内部の損失補正回路

図5:コネクタ内部の損失補正回路 図6:高周波成分が信号の立ち上がりを早くする

図6:高周波成分が信号の立ち上がりを早くする 図7:デエンファシス

図7:デエンファシス 表1:PCI Express規格(出力フィルタ規格):PCI Express Basic Specification Revision 3.0 Noverber 10,2010

表1:PCI Express規格(出力フィルタ規格):PCI Express Basic Specification Revision 3.0 Noverber 10,2010