第40回 IBIS AMI:前田真一の最新実装技術あれこれ塾(3/4 ページ)

3.SPICEモデルによる解析

IBISモデルでの対応が難しいフィルタの特性、プリエンファシスの解析、入力特性と出力特性を持ったリピータの解析などはSPICEシミュレータで可能です。

SPICEシミュレータを基にして開発された伝送線路シミュレータは多くあります。しかし、これらの伝送線路解析の多くは、伝送線路解析に必要ない機能を削ったり、IBISモデルに最適化したり、伝送線路解析に便利な機能を加えたりしています。

このため、伝送線路解析の多くは、フィルタやリピータの解析はできません。しかし、SPICEシミュレータで、それ専用のモデルだけでなく、IBISモデルが使えるようにしたもののも多くなってきました。

IBISモデルでもプリエンファシスの解析ができるような機能強化としてVersion 4からVerilog-AMS(Analog Mixed Signal)やVHDL-AMSと呼ばれるシミュレータをサポートする機能が追加されました。

SPICEやAMSは機能的にはPCI Expressをはじめとするシリアル伝送回路の解析に使えます。しかし、問題は解析時間にあります。

解析スピードを早くすることは、当初、IBISモデルを開発した大きな目的の1つでした。そしてその目標は達成されていました。例えば、IBIS Vwesion 5で追加された電源電圧変動と信号を同時に解析する手法では、IBISモデルでの解析時間は18分であるのに対し、SPICEでは最大33時間近くかかっています(注2)。

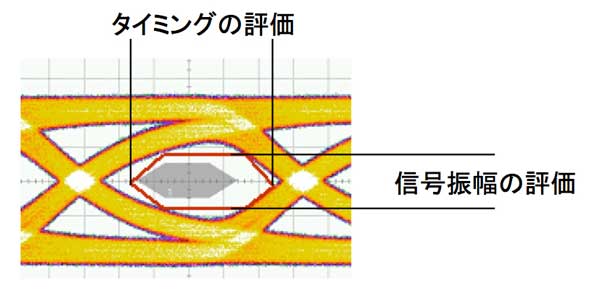

つまり最大で、100倍以上の解析の高速化ができるのです。高速シリアル伝送(シリアルリンク)ではクロックとデータを合成して送るので、多くのビットパターンを連続して解析しアイパターン(Eye Pattern)で結果判定をします(図16)。

クロック信号のように規則正しい周期信号(図17)では、同じデータの繰り返しになるため、数周期の解析を行えば、それ以上の解析を行っても電源電圧変動やランダムジッタなどの外的要因を除いては、結果は変わりません。

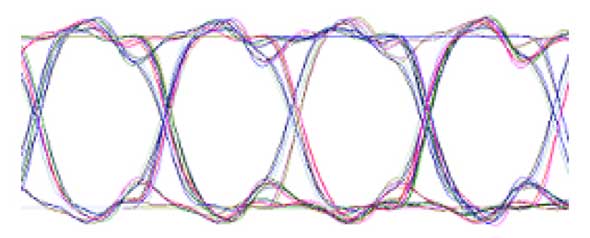

それに対して、データはビット列がランダムに変化します(図18)。

このようにビットパターンが変化する信号の場合、特に信号が高速になればなるほど信号パターンによって波形ゆがみが変化します。

これは、信号が立ち上がりきらないうちに変化したり、オーバーシュートの途中でデータが変化したりと信号が完全に安定する前にデータが変化するからです(図19)。

このようにデータパターンによって波形が変化するノイズをISI(Inter Symbol Interference:符号間干渉)と呼びます。

このような信号の波形解析では、あらゆるビットパターンの組み合わせを解析しないと正しい解析結果が得られません。

シミュレーションでは一定の長さのデータ列で、ランダムに発生するビットパターンの組み合わせを解析するために疑似ランダム・ビット・シーケンス(PRBS=Pseudo Random Bit Sequence)と呼びます。

通常、このPRBSのビット列は長さ2n-1でn=8〜10(255〜1023ビット)程度が使われます。

このため、シリアル転送方式のSI解析では膨大なビット数のデータを解析する必要があります。

例えば、1つの条件で1000ビットを解析する必要があれば、ジッタや電源電圧変動、その他の条件を組み合わせれば、数万ビットの解析を行う必要が出てきます。

実際、PCI Express規格ではビットエラーレート(BER=Bit Error Rate)と呼ばれる規格があります。これは、ある決められたビット数を転送して、「転送エラーが何ビット以下でなければならない」とする規格です。PCI Expressの規格では、1012ビットのデータ転送を行って、データエラーが1ビット以下でなければならないと要求しています。

つまり、規格を満足するかどうかをシミュレーションするためには1012ビットのシミュレーションを行う必要があるわけです。

SPICEシミュレーションは解析速度が遅いので、200ビット程度の解析を行うだけで、数分〜数時間かかってしまいます。これでは、1012ビットの解析を実行することは事実上、不可能です。それどころか、IBISモデルを使った解析でもこのように大量の解析は実現不能です。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 日本が再び世界をリードするための、“シン”モノづくりの世界

- 自動車工場で聞こえるのに、食品工場では聞こえない音〜工場の主人公は誰か

- 「自動車以外は全て好調」、四半期受注過去最高のDMG森精機が通期予想上方修正

- エンジニアリング業務を自律実行、シーメンスが産業AIを新たな段階に

- マグネットで触れるだけ、振動値を5秒で判定する回転機振動チェッカー

- 「ロボット大国」日本の逆襲、地道なモノづくりが世界を動かす交渉力に

- 猛暑に備えて

- 工場の主人公は誰なのかという問いかけ、元トヨタ生技が見た食品工場のなぜ

- ヒューマノイド中核部品がハノーバーメッセ技術賞、“脱自動車”のシェフラー開発

- 防衛事業の生産体制強化、ソナーなど水中音響センサーの新生産棟を建設

コーナーリンク

図16:Eye Patternによる波形の判定

図16:Eye Patternによる波形の判定 図17:周期信号(クロック信号)

図17:周期信号(クロック信号) 図18:データ信号

図18:データ信号 図19:ISI

図19:ISI