第7回 銅の限界:前田真一の最新実装技術あれこれ塾(3/3 ページ)

TSV(Through Silicon Via)を使ったMCM技術はシリコンフォトニクスによる光素子とCMOS論理ICの統合を安価に実現し、光時代を拓く可能性が高いことはすでに紹介しました(第5回 光と銅)。

しかし、TSVは銅による高速信号伝送にとっても有効な技術なのです。シリコン基板は誘電率や誘電正接をFR4よりも小さくし、非常に平坦な銅配線を実現することが可能となります。シリコン自体の誘電率は3.5〜4.5と大きいのですが、酸化シリコンとなると誘電率は1.6と小さくなります。基板材料としての可能性があるのです。

これらの損失を低減させるための対策は大きな効果はありますが、損失は本質的なもので、なくすことはできません。信号の周波数が高くなれば、損失は大きくなります。

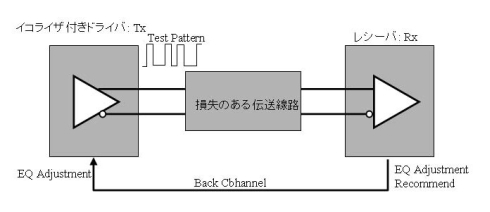

そこで、回路的に損失で失われる周波数の高い成分だけ大きくして損失で失われる分を補正してやる手法はPCI Expressを始め多くのシリアル伝送規格で標準的に使われています(図10)。

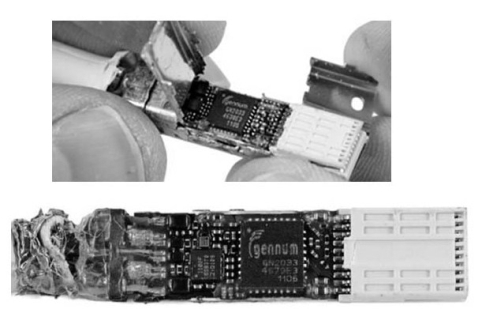

図10 Thunderboltケーブル(クリックで拡大)(出典:Ifixitl http://www.ifixit.com/blog/blog/2011/06/29/what-makes-the-thunderbolt-cable-lightning-fast/)

図10 Thunderboltケーブル(クリックで拡大)(出典:Ifixitl http://www.ifixit.com/blog/blog/2011/06/29/what-makes-the-thunderbolt-cable-lightning-fast/)Apple社が出荷したThunderboltのケーブルでは、コネクタ内部に周波数に応じて信号のレベルを変化させるイコライザICが内蔵されています(図11)。この工夫によって10Gbpsの高速データ転送が銅線でも可能になったのです。

減衰は配線の長さによって変化しますので、あらかじめ配線の長さが分かっている場合は良いのですが、配線の長さが判らない場合にはすべての周波数の信号振幅を揃えることは困難です。

PCI ExpressのGen3では、はじめにテストパターンを伝送し、レシーバが受け取った信号をフィードバックすることにより、ドライバ側の周波数による出力特性を変化させ、レシーバ側で全ての周波数にわたって最適な信号レベルのデータが受け取れるようにしました。

このような回路的な工夫は、LSIの集積度の向上に従い、非常に複雑な回路でもコストアップ無しにICに組み込むことができます。

このままでは、コストアップなしに銅での伝送速度はまだまだ上げられそうですが、これ以上信号が大きくなり損失が大きくなると、新しい問題が発生します。損失を補うような大きなレベルで信号を送るためには、ドライバICの電源電圧を高くする必要があります。電力は電圧と電流の積なので、電圧が高くなると信号の電力が増大します。

これは、ICの消費電力を向上させると同時に信号からの電磁放射ノイズを増大させます。また、電力の増大は同時スイッチングノイズ(SSOノイズ、SSN)の増大、発熱の増大、モバイル機器の電池駆動時間の短縮など、多くの問題を引き起こします。

これらの対策には多くの費用が掛かり、光の方がコスト的に有利になる可能性があります。これが、光と電気の境目です。

しかし、電気側は、この問題を解決するために、これまで使われてきたLVDSドライバ回路に変わる超低電流駆動ドライバ回路を開発しています。

詳細は分かりませんが、『Energy Efficient Scalable I/O』(ESSI)と呼ばれるドライバ回路はLVDSドライバ回路の1/10以下の電力でデータを転送できるとのことです(※2)。

(※2)PC Watch 【Research@Intel 2010レポート】

このような回路技術や新しい材料、製造技術が実用化されれば、また、光の時代は先送りされるかもしれません。

筆者紹介

前田 真一(マエダ シンイチ)

KEI Systems、日本サーキット。日米で、高速システムの開発/解析コンサルティングを手掛ける。

近著:「現場の即戦力シリーズ 見てわかる高速回路のノイズ解析」(技術評論社)

関連記事

第6回 Thunderbolt

第6回 Thunderbolt

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第6回は、第4回、第5回で紹介してきた「Thunderbolt」について、さらに踏み込んで解説する。 第5回 光と銅

第5回 光と銅

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第5回は、光インタフェースと、銅を使う電気インタフェースのメリットとデメリットについて紹介する。 第4回 Light PeakからThunderbolt

第4回 Light PeakからThunderbolt

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第4回は、新しいI/Oインタフェーステクノロジーとして注目されている「Thunderbolt」について紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 軸受業界再編へNSKとNTNが経営統合に基本合意、両トップが語った危機感とは

- なぜオムロンは農業の“作業”ではなく“判断”の自動化を目指すのか

- 日本が再び世界をリードするための、“シン”モノづくりの世界

- 接触前に停止する協働ロボットに18kg可搬が登場、動作範囲も拡張

- 「自動車以外は全て好調」、四半期受注過去最高のDMG森精機が通期予想上方修正

- 成功率90%超でコンテナ搬送、ヒューマノイドをシーメンス工場に試験導入

- 最大26kWの超高出力化が可能、アマダが新たなファイバーレーザーマシン

- オムロンの制御機器事業が「再成長」に転換、M&Aで欧米顧客基盤を強化へ

- ヒューマノイド導入を支援するコントローラー、既存手法とVLAモデルを統合

- オムロンが電子部品事業を米国投資会社に売却、新会社名はAratasに

コーナーリンク