共通クロック・インターフェイスの制約を学ぶ:必修! FPGAタイミング解析の基礎(3)(3/3 ページ)

クロック入力が複数の場合

次は少し応用的な場合を考えてみましょう。FPGAに複数のクロックが入力されていて、それぞれに対して、異なるセットアップとホールド時間が定義されている場合です。

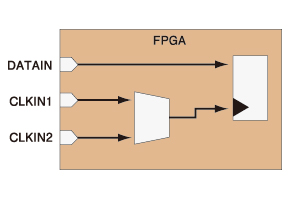

図6に示す回路は、CLKIN1とCLKIN2の2つのクロックが入力され、FPGA内で切り替えることができます。周波数は100MHzと125MHzとします。DATAINはCLKIN1または、CLKIN2に同期したデータ入力です。セットアップとホールド時間が、2つのクロックに対して異なる値となっています。この回路に対する正しいタイミング制約はどのようなものでしょうか?

| クロック周波数 | クロック周期 | DATAIN セットアップ時間 |

DATAIN ホールド時間 |

|

|---|---|---|---|---|

| CLKIN1 | 100Hz | 10ns | 2.5ns | 1.0ns |

| CLKIN2 | 125Hz | 8ns | 3.0ns | 0.5ns |

| 図6 回路例 | ||||

まず、クロックを定義することから始めます。FPGAの入力クロックと、それに対応する仮想クロックを定義します。クロックがマルチプレクスされている場合は、「set_clock_group」コマンドを使って、排他関係にあることを示す必要がありました(分かりにくい場合は、第2回を読み直してみてください)。

create_clock -name clkin1 -period 10 [get_ports CLKIN1]

create_clock -name vclk1 -period 10

create_clock -name clkin2 -period 8 [get_ports CLKIN2]

create_clock -name vclk2 -period 8

set_clock_groups -exclusive -group {clkin1 vclk1} -group {clkin2 vclk2}

次に、「FPGAスペックが決まっている場合の入力制約」の考え方を使って、CLKIN1に対して入力のタイミング制約を行います。次のように [] 内で「expr 数式」と書くと、数式の計算結果を書いたのと同じ意味になります。

set_input_delay -clock vclk1 -max [expr 10.0 - 2.5] [get_ports DATAIN] set_input_delay -clock vclk1 -min 1.0 [get_ports DATAIN]

同じように、CLKIN2に対して入力のタイミング制約を行います。CLKIN1の場合とほとんど同じですが、「-add_delay」オプションが必要になります。このオプションは、上で与えた制約を置き換えずに、新たに制約を追加することを意味します。

set_input_delay -clock vclk2 -max [expr 8.0 - 3.0] [get_ports DATAIN] -add_delay set_input_delay -clock vclk2 -min 0.5 [get_ports DATAIN] -add_delay

このように、2種類のクロックとそれらに対する入力制約を同時に指定することができます。FPGAの開発ツールは両方の制約を満たすように、論理合成や配置配線を行います。また、両方の制約に対するタイミング解析が行われます。

SDC文法のまとめ

今回の解説の中で使用したSDCコマンドの文法を簡単にまとめておきます。

次回は、ソース・シンクロナス方式のインターフェイスのタイミング制約方法を解説します。(次回に続く)

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 40台超のロボットを統合管理する自律運用システムが本格稼働

コーナーリンク