共通クロック・インターフェイスの制約を学ぶ:必修! FPGAタイミング解析の基礎(3)(1/3 ページ)

今回はI/Oタイミングの制約について解説する。まずは共通クロック・インターフェイスの制約について押さえよう。

前回は、SDCによる具体的な制約記述として、クロックの制約方法について解説をしました。今回は、I/Oタイミングの制約について解説します。

デバイス間のインターフェイス方式は?

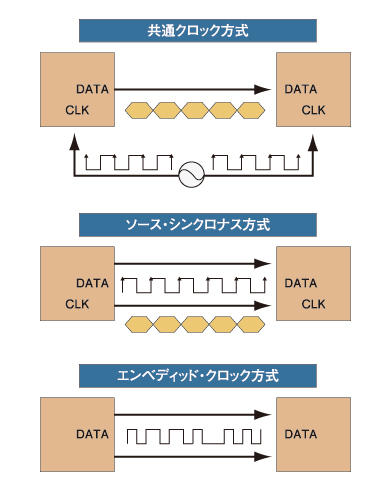

FPGAなどのデバイス間のインターフェイス方法として、さまざまなプロトコルが規定されています。タイミングという観点で見ると、これらのインターフェイス方式は3つのタイプに分類できます(図1)。

- 共通クロック方式

送受信のデバイスに共通のクロックを分配して、クロックに同期させたデータの転送を行います。PCIなど、レガシーのパラレル・バスの多くはこの方式です。データの転送レートが、物理的な遅延の制約を受けるので、あまり高速で動作させることはできません。150Mbps程度が限界となります。今回の解説では、共通クロック方式のタイミング制約について扱います。 - ソース・シンクロナス方式

送信デバイスがデータとともにクロックを送り出し、受信デバイスはこのクロックでデータを取り込む方式です。単純な回路で、比較的高速なデータ転送が可能になるため、非常によく使われます。LVDS、GMII、DDR(2/3)-SDRAMなどがこの方式です。

共通クロックと違い、クロックとデータの遅延が打ち消し合うので、物理的な遅延がデータ転送レートの制約にはなりません。LVDSやDDR3-SDRAMを1Gbpsで動作させることのできるデバイスもあります。ソース・シンクロナス方式のタイミング制約は次回に解説する予定です。 - エンベディッド・クロック方式

ソース・シンクロナス方式では、クロックとデータ間のスキューが高速化のネックになります。この問題を解決するために、クロックをデータに埋め込んで転送する方式です。データをエンコードすることで、クロックの成分を埋め込みます。

受信デバイスがデータからクロックを生成して、データの取り込みに使います。PCI Express、XAUIなど、いわゆるSerDesを使ったプロトコルはこの方式です。5〜6Gbps以上を実現することができます。通常は、スタティック・タイミング解析や、論理合成の対象ではないため、この解説では扱いません。

I/Oのタイミング制約

大切なのは、与えられた設計条件から、I/Oのタイミング制約を正しく導き出すことです。普通は、周辺デバイスなど、FPGA外部のACスペックが先に決まっているので、これが設計条件として与えられます。逆にFPGA自体のACスペックが設計条件となる場合もあります。

どちらかを理解できれば、もう一方へは変換するだけですから、それほど難しくありません。I/Oのタイミング制約は周辺デバイスを含むシステムで考えます。FPGA外部のACスペックからの方が考えやすいので、最初にその場合について説明をします。続いて、FPGAのスペックを基にした場合について考えていきます。

共通クロック方式の入力制約

まず、FPGA外部のACスペックが決まっている場合の、入力制約の考え方です。

入力制約には、「set_input_delay」というコマンドを使います。このコマンドは、FPGAの入力ポートでのデータの到着時間を制約します。次のように、最大と最小の制約をセットで使います。

set_input_delay -clock vclk -max <最大データ遅延時間> [get_ports DATAIN] set_input_delay -clock vclk -min <最小データ遅延時間> [get_ports DATAIN]

- 「-clock」オプションは、基準となるクロックの定義名を指定します。前回説明した「create_clock」コマンドで、仮想クロックを定義して使います。

- 「-max」オプションは、データの最大遅延時間を指定します。基準クロック後にデータが到達する最大の時間です。この制約が入力のセットアップ解析に使われます。

- 「-min」オプションは、データの最小遅延時間を指定します。基準クロック後にデータが到達する最小の時間です。この制約が入力のホールド解析に使われます。

- 最後に遅延時間を定義する対象の入力ポートを指定します。

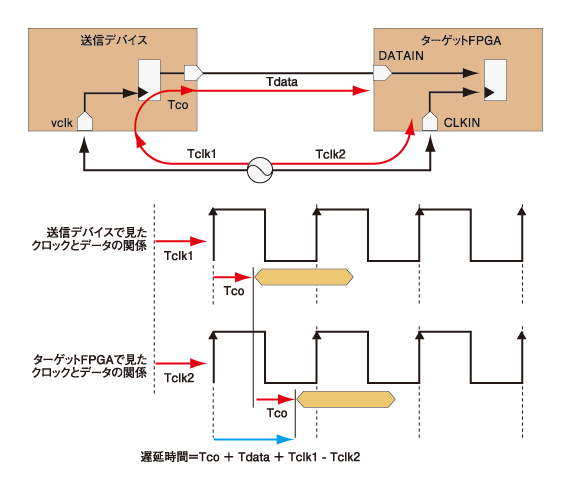

ここではデータ遅延時間の値をどのように決めるかが問題です。FPGA外部のACスペックは、図2に示すとおりです。送信デバイスの出力遅延(Tco)、データの伝搬遅延(Tdata)、送信デバイスへのクロックの伝搬遅延(Tclk1)、ターゲットFPGAへのクロックの伝搬遅延(Tclk2)が分かっています。

データ遅延時間は、FPGAの入力ポートで、送信デバイスのクロックに対して定義します。送信デバイスのクロックは、FPGA内にはないので仮想クロックとして定義しておきます。図2のタイムチャートから分かるように、次の式のようになります。

<データ遅延時間> = Tco + Tdata + Tclk1 - Tclk2

これを最大と最小の場合に分ければ完成です。区別のために、それぞれの最大値には「_max」、最小値には「_min」を付けることにすると、次のようになります。最後の項はマイナスのため、最大と最小が入れ替わっているので注意してください。

<最大データ遅延時間> = Tco_max + Tdata_max + Tclk1_max - Tclk2_min <最小データ遅延時間> = Tco_min + Tdata_min + Tclk1_min - Tclk2_max

具体的な数値例を入れると、図2の回路に対する制約は次のようになります。2行目はFPGAへの入力クロックと、それと同じ周波数、位相の仮想クロックを定義しています。これは送信デバイスのクロックと考えることができ、このクロックを基準に入力の制約を与えています。

create_clock -name clkin -period 10 [get_ports CLKIN] create_clock -name vclk -period 10 set_input_delay -clock vclk -max 5 [get_ports DATAIN] set_input_delay -clock vclk -min 2 [get_ports DATAIN]

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- 40台超のロボットを統合管理する自律運用システムが本格稼働

コーナーリンク

図1 タイミングという観点で見た、インターフェイス方式の分類

図1 タイミングという観点で見た、インターフェイス方式の分類 図2 FPGA外部のACスペックとタイムチャート

図2 FPGA外部のACスペックとタイムチャート