「MAX 10 NEEK」に搭載されたDDR3メモリを使う:MAX 10 FPGAで学ぶFPGA開発入門(10)(2/6 ページ)

MAX 10 NEEKに搭載されたDDR3メモリを使う

さて、今回はNEEKに搭載されたDDR3メモリを使ってみたい。MAX 10 NEEKには、FPGA内に内蔵されたSRAMとは別に、外部にDDR3メモリが搭載されている。DDR3/LPDDR2のI/FはMAX 10に標準搭載されており、なので基本DDR3ないしLPDDR2を搭載すればMAX 10からこれを利用する事ができる。もちろん、NIOS IIからの利用も可能だ。

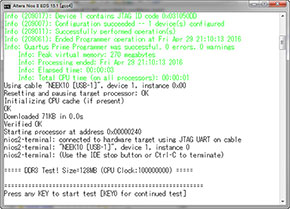

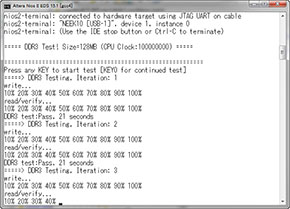

MAX 10 NEEKのSystem CDを展開すると、Demonstrations\ddr3_niosの下に、NIOS IIからDDR3をアクセスするためのサンプルコードが用意されている。まずは手始めに、MAX 10 NEEKを起動してUSB Blaster IIを接続した状態で、Demonstrations\ddr3_nios\demo_batchの下にあるddr3_nios.batを起動すると、こんな画面になるはずだ(Photo02)。KEY0を押すと、NIOS IIからDDR3メモリへの読み書きがテストが開始される(Photo03)。問題がなければ、test結果は“Pass”になる。

このdemo_batchの下はバイナリの形で提供されているので、これを自分でビルドしなおしてみよう。

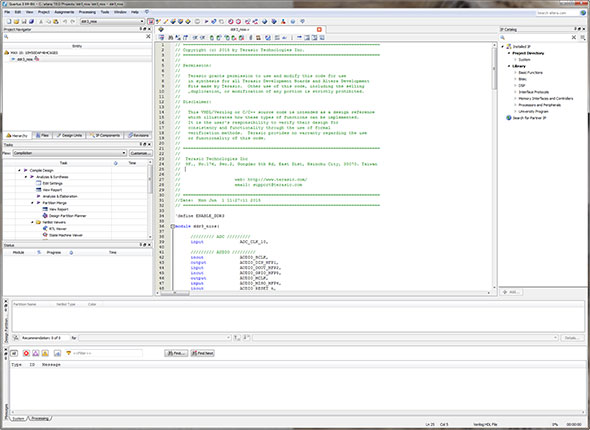

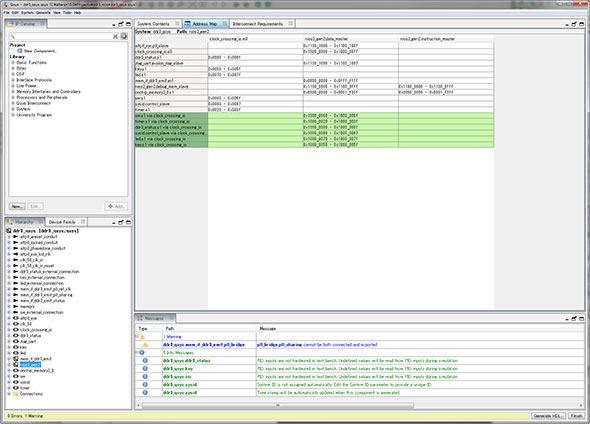

Demonstrations\ddr3_nios の下を丸ごと他のフォルダにコピーして、Quartus IIから"File" → "Open Project..."でddr3_nios.qpfを選択してプロジェクトを開く(Photo04)。そのままコンパイルしてもいいのだが、構成を確認するためにQSYSを開いてみる(Photo05,06)。

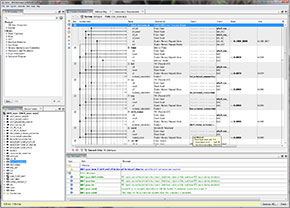

メモリマップはこんな感じ(Photo07)で、0x08000000〜0xfffffffにDDR3メモリがマッピングされていることが分かる。マッピングを見る限り、スタックとかダイナミックな変数にDDR3の領域を使うのは、そのままでは無理(EclipseでC++のソースのビルドの際にリンクオプションで設定をしない限り自動では使ってくれない)だが、プログラム内からアドレスを指定して利用するのは問題なさそうだ。

関連記事

「MAX 10 NEEK」へソフトコアCPUを組み込む

「MAX 10 NEEK」へソフトコアCPUを組み込む

周辺機器の充実したMAX10搭載開発ボード「MAX 10 NEEK」に、ソフトコアCPU「NIOS II」を組み込み、ソフトコアCPUからボード搭載LEDの制御までを紹介する。 周辺機器の充実した「MAX 10 NEEK」で本格的な開発を目指す

周辺機器の充実した「MAX 10 NEEK」で本格的な開発を目指す

FPGA開発において周辺機器(回路)は見落とせない要素の1つ。タッチパネルや各種出入力などを備えた「MAX 10 NEEK」を導入して、本格的な開発を目指す。 FPGAのソフトコアCPUをベンチマークで測定する

FPGAのソフトコアCPUをベンチマークで測定する

FPGA「MAX10」に「NIOS II」と呼ばれるソフトIPコアを導入することで、ソフトコアCPUを構築できる。ではその処理能力はどれほどか。ベンチマークソフトで測定してみよう。 FPGA上でソフトコアCPUを動かす手引き

FPGA上でソフトコアCPUを動かす手引き

これまでFPGAの開発基礎としてLチカなどを紹介してきたが、今回はちょっと目先を変えてFPGA上でのCPUコア動作に取り組む。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 よろしいならばダイナミック点灯だ――FPGAでLEDをダイナミックにLチカさせる

よろしいならばダイナミック点灯だ――FPGAでLEDをダイナミックにLチカさせる

単純なLチカならばFPGAでもそう難しくない。ただ、ダイナミック点灯やそれに伴うソースの最適化については“ならでは”のポイントが散見される。今回も連載で利用している「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 FPGAのLED制御プログラムを深く理解する

FPGAのLED制御プログラムを深く理解する

FPGA開発に必要なHDLへの理解を深めるため、MAX 10に用意されているArduino I/Oを利用してのLチカを行い、多灯LEDの制御を含めたプログラミングも解説する。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 40台超のロボットを統合管理する自律運用システムが本格稼働

コーナーリンク