「MAX 10 NEEK」に搭載されたDDR3メモリを使う:MAX 10 FPGAで学ぶFPGA開発入門(10)(4/6 ページ)

Generate HDLで構成を生成

もろもろ確認したら、Generate HDLを押して構成を生成する。この際にPhoto14にもあるようにWarningが出ているが、これはQuartus IIというかQSYSの既知の問題(pll_sharing Warning Message May Appear)なので、無視して差し支えない。

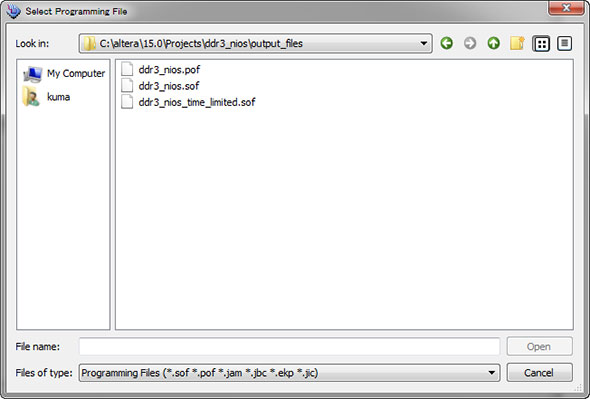

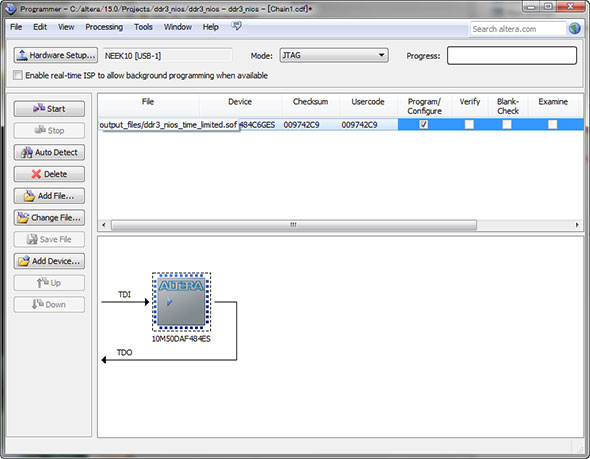

HDLの生成が終わったらQuartus IIに戻ってコンパイルを行う(Photo15)。その後にはプログラミングであるが、Programmerから"Add File..."を選ぶと見慣れないファイルがあるはずだ(Photo16)。これは第9回(「MAX 10 NEEK」へソフトコアCPUを組み込む)でもちょっと触れたが、Nios II/fは有償であり、そのままでは利用できないためだ。

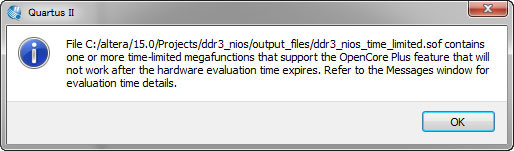

開発用にはOpenCore Plusベースのものが利用できるが、こちらは時間制限付きとなっている。ファイル名に“time_limited”がついているのはこのためだ。この"_time_limited"付を選ぶと、こんな警告メッセージ(Photo17)が出てくるのでOKを押して、そのままMAX 10にロードする(Photo18)。

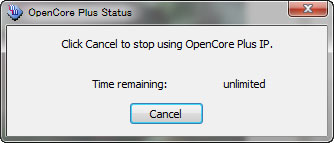

ロードが終わるとダイアログが表示される(Photo19)が、これがTime Limitedの制約である。今はUSB Blaster経由でロードしているから、このダイアログを表示させている間はずっとNios II/fを使い続けられるという意味で、ここでCancelを押すとNios II/fが利用できなくなる。なので、Cancelを押さずに次に移る。

関連記事

「MAX 10 NEEK」へソフトコアCPUを組み込む

「MAX 10 NEEK」へソフトコアCPUを組み込む

周辺機器の充実したMAX10搭載開発ボード「MAX 10 NEEK」に、ソフトコアCPU「NIOS II」を組み込み、ソフトコアCPUからボード搭載LEDの制御までを紹介する。 周辺機器の充実した「MAX 10 NEEK」で本格的な開発を目指す

周辺機器の充実した「MAX 10 NEEK」で本格的な開発を目指す

FPGA開発において周辺機器(回路)は見落とせない要素の1つ。タッチパネルや各種出入力などを備えた「MAX 10 NEEK」を導入して、本格的な開発を目指す。 FPGAのソフトコアCPUをベンチマークで測定する

FPGAのソフトコアCPUをベンチマークで測定する

FPGA「MAX10」に「NIOS II」と呼ばれるソフトIPコアを導入することで、ソフトコアCPUを構築できる。ではその処理能力はどれほどか。ベンチマークソフトで測定してみよう。 FPGA上でソフトコアCPUを動かす手引き

FPGA上でソフトコアCPUを動かす手引き

これまでFPGAの開発基礎としてLチカなどを紹介してきたが、今回はちょっと目先を変えてFPGA上でのCPUコア動作に取り組む。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 よろしいならばダイナミック点灯だ――FPGAでLEDをダイナミックにLチカさせる

よろしいならばダイナミック点灯だ――FPGAでLEDをダイナミックにLチカさせる

単純なLチカならばFPGAでもそう難しくない。ただ、ダイナミック点灯やそれに伴うソースの最適化については“ならでは”のポイントが散見される。今回も連載で利用している「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 FPGAのLED制御プログラムを深く理解する

FPGAのLED制御プログラムを深く理解する

FPGA開発に必要なHDLへの理解を深めるため、MAX 10に用意されているArduino I/Oを利用してのLチカを行い、多灯LEDの制御を含めたプログラミングも解説する。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- 40台超のロボットを統合管理する自律運用システムが本格稼働

コーナーリンク