第21回 装置の電源:前田真一の最新実装技術あれこれ塾(3/3 ページ)

5. パスコン

LSIの消費電力増大と信号の高速化はLSIの電源電圧変動を大きな問題点としました。

問題が大きくなった原因は以下の3つあります。

- LSIの消費電力増大と信号の高速化により、電源変動が大きくなった

- 信号の高速化とLSIの電源電圧の低圧化により、電源電圧変動の影響が大きくなった

- 信号の高速化により、対策が困難になった

この電圧が変動してから、電源電圧がもとに戻るまでの間、負荷であるLSIの電源電圧を変動させないようにバイパス・コンデンサを使います。電源電圧の変動を抑える方法はコンデンサを使用するのが最も効果的な方法です。

コンデンサが電源電圧の変動を抑える働きは、どちらも同じことなのですが、電荷の移動とインピーダンスの2通りで説明されます。

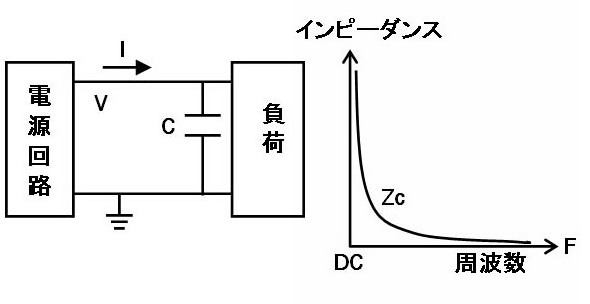

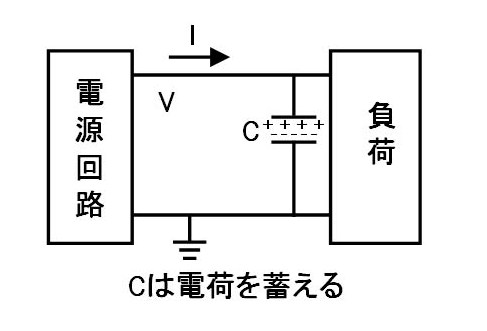

LSIの電源ピンとグランドピンの間にコンデンサを挿入します(図6)。電源電圧が安定している時には直流なので、コンデンサのインピーダンスは無限大で電流は流れません。このとき、コンデンサの内部には安定した電荷が蓄えられています(図7)。

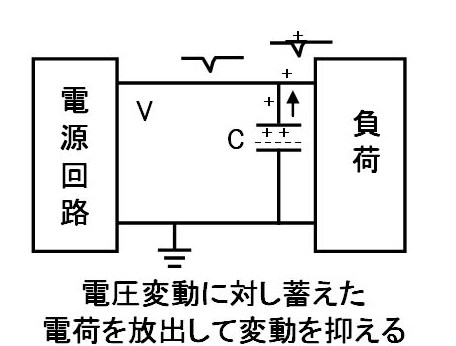

電源電圧が急激に変化すると、コンデンサは内部の電荷を放出して電源電圧の変化を阻止します(図8)。

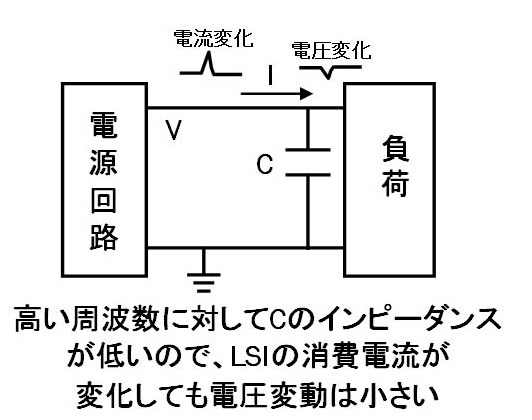

インピーダンスでいえば、急激な電源電圧の移動は、非常に高い周波数で電源電圧が変動することです。高い周波数の変動に対してはコンデンサのインピーダンスは非常に低くなるので、電流が流れても電圧変動は小さなものとなります(図9)。

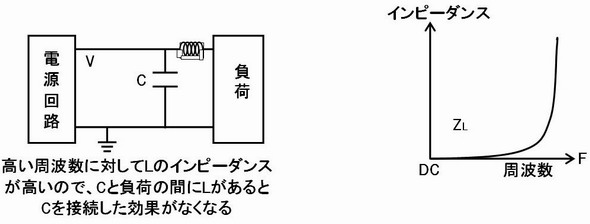

ここで問題となるのはLです。Lは周波数が高くなるとインピーダンスが大きくなるので、配線やコンデンサ部品がL成分をもつと、電源電流の変化に対して大きな電圧降下を発生させます(図10)。

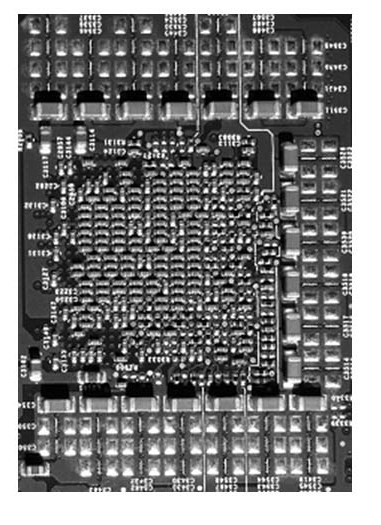

LSIの消費電力の増大と動作の高速化はパスコンによる電源変動抑圧効果を著しく困難にしています。LSIの消費電力増大により、LSIに流れる電流の変化が大きくなります。個の大きな電流変化をパスコンが貯めている電荷で補正するためには大きな容量が必要となります。 単純に容量の大きなコンデンサは、応答時間が遅く、高速LSIの電源電圧補正には間に合わないので、高速応答できる、容量に小さなコンデンサを大量に使用する必要があります。

最近のLSIでは電源電圧が多様化してきて、そのおのおのに大量のパスコンを使う必要があります。このため、1個のLSIに対して数百個のパスコンを搭載するようになっています(図11)。

LSI信号の高速化によって信号の変化によって生じる電源電圧変動も高速化しています。このため、部品としてのコンデンサもより高速動作するような製品が次々と開発されています。

また、基板設計でもバイパスコンデンサの配置、配線に対しては細かいところまで研究がなされ、詳細な設計指示がされています。電源電圧の変化はLSIの動作に影響を与えるので、LSIチップへの供給電位が安定する必要があります。

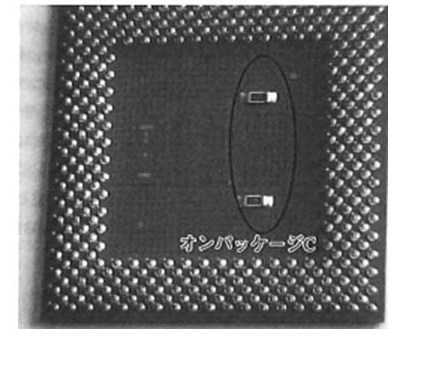

しかし、基板上に配置されたバイパスコンデンサはICパッケージの部品便の電位を安定させますが、パッケージの内部やパッケージからICチップへの接続経路で発生する電源電圧変動要素に対しては効果がありません。

このため、パッケージ内の配線基板(インタポーザ)にパスコンが配置されるようになりました(図12)。インタポーザ基板は小さく、多くのパスコンを配置する余裕がないため、部品内蔵基板が使われたりします。部品内蔵基板は配線によるL成分が小さくでき、パスコンが高い周波数まで効果をもつようにもできます。

せっかく高価な部品内蔵基板を使っても、マザーボードでは、パスコンが高い周波数まで有効になるという部品内蔵基板の特徴の一つはあまり生かされません。

基板埋め込み基板は価格の点もありますが、マザー基板にはあまり使われず、インタポーザやモジュール基板により多く使われている理由です。

4. 電源の来たるべき姿

さらに次の段階としては電源をパッケージに配置することが考えられます。

オンPCBコンデンサよりもオン・パッケージコンデンサの方がLSIチップまでの経路が短く、経路のL成分が小さくなります。このため、オン・パッケージCは高い周波数のノイズに対して効率がよいわけです。

それならば、コンデンサではなく、パッケージの上に電源回路を配置すれば、PDNはオンボード電源よりもずっと効率が良くなります。

一つのパッケージの中に複数のチップを実装するSiP (System in Package)化が進んでいます。

例えば、新しいDDRメモリであるDDR4やWide I/O規格では、1パッケージに複数のメモリチップを内蔵することが規格として盛り込まれています。

複数のチップを1パッケージに内蔵することにより、パッケージの消費電力が増大するため、チップへの電源供給がこれらの規格では強化されています。これらSiPの電源供給は、パッケージの内部に電源回路をもってくれば、解決します。

パッケージ内に配置するためには電源回路を小型化する必要があります。部品内蔵基板は有効なソリューションとなります。

しかし、さらに究極の解決のため、ICチップ内に電源回路を集積してしまう手法が開発されつつあります。

筆者紹介

前田 真一(マエダ シンイチ)

KEI Systems、日本サーキット。日米で、高速システムの開発/解析コンサルティングを手掛ける。

近著:「現場の即戦力シリーズ 見てわかる高速回路のノイズ解析」(技術評論社)

関連記事

- ≫前田真一の最新実装技術あれこれ塾

第20回 部品の内層実装

第20回 部品の内層実装

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第20回は、日本が伝統的に世界で優位に立っている実装技術「部品内装基板」について解説する。 第19回 CADデータの統合とPLM

第19回 CADデータの統合とPLM

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第19回は、協調設計とCADデータの重要性や、設計を並行して進めるコンカレントエンジニアリング、PDMとPLMなどについて解説する。 第18回 CADデータの統合

第18回 CADデータの統合

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第18回は、電子機器を設計する際のCAD/CAEソフトの必要性や、「ハードとソフト」「メカと電気」の協調設計の重要性について解説する。 第17回 CAD/CAMデファクト・スタンダード

第17回 CAD/CAMデファクト・スタンダード

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第17回は、ガーバデータをはじめ、プリント基板設計技術者にとってデファクト・スタンダード(業界標準)となっているCAD/CAMツールのデータ形式について解説する。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 日本が再び世界をリードするための、“シン”モノづくりの世界

- 自動車工場で聞こえるのに、食品工場では聞こえない音〜工場の主人公は誰か

- 「自動車以外は全て好調」、四半期受注過去最高のDMG森精機が通期予想上方修正

- エンジニアリング業務を自律実行、シーメンスが産業AIを新たな段階に

- マグネットで触れるだけ、振動値を5秒で判定する回転機振動チェッカー

- 「ロボット大国」日本の逆襲、地道なモノづくりが世界を動かす交渉力に

- 猛暑に備えて

- 工場の主人公は誰なのかという問いかけ、元トヨタ生技が見た食品工場のなぜ

- ヒューマノイド中核部品がハノーバーメッセ技術賞、“脱自動車”のシェフラー開発

- 防衛事業の生産体制強化、ソナーなど水中音響センサーの新生産棟を建設

コーナーリンク

図6 コンデンサの挿入

図6 コンデンサの挿入 図7 コンデンサに電荷を蓄える

図7 コンデンサに電荷を蓄える 図8 コンデンサが電荷を放出

図8 コンデンサが電荷を放出 図9 インピーダンスが低いと電圧変動は小さい

図9 インピーダンスが低いと電圧変動は小さい 図10 インダクタはコンデンサとLSIの接続を遮断する

図10 インダクタはコンデンサとLSIの接続を遮断する 図11 LSIには多くのコンデンサを接続

図11 LSIには多くのコンデンサを接続 図12 パッケージ上のパスコン

図12 パッケージ上のパスコン