ソニーの裏面照射型CMOSセンサーが「3階建て」に、飽和信号量2倍でDR拡大:組み込み開発ニュース

ソニーセミコンダクタソリューションズは「世界初」(同社)の2層トランジスタ画素積層型CMOSイメージセンサー技術を開発した。光を電気信号に変換するフォトダイオードと信号を制御するための画素トランジスタの層を別々の基板に形成し積層することで、従来の裏面照射型CMOSイメージセンサーと比べて約2倍の飽和信号量を確保した。

ソニーセミコンダクタソリューションズは2021年12月16日、「世界初」(同社)の2層トランジスタ画素積層型CMOSイメージセンサー技術の開発に成功したと発表した。光を電気信号に変換するフォトダイオードと信号を制御するための画素トランジスタの層を別々の基板に形成し積層することで、従来の裏面照射型CMOSイメージセンサーと比べて約2倍の飽和信号量を確保した。これによる、ダイナミックレンジの拡大とノイズの低減を実現できるため、より高画質な撮影が可能になるという。

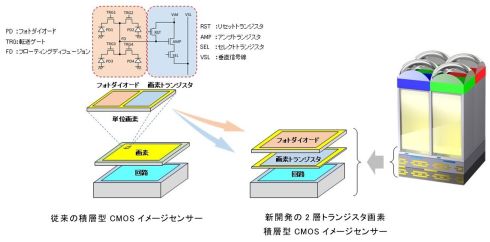

同社の裏面照射型CMOSイメージセンサーは、裏面照射型画素が形成された画素チップと信号処理回路が形成されたロジックチップを重ね合わせた積層構造を特徴としている。この積層型CMOSイメージセンサーは、それまでの裏面照射型CMOSイメージセンサーが画素部と信号処理回路部を1枚のシリコン基板で構成していた「1階建て」から、画素チップと信号処理回路の2枚のシリコン基板に分けた「2階建て」とすることで、多機能化による回路規模の増加や構造の小型化を実現した点が高く評価された。これによって、同社のイメージセンサー市場のシェア向上に貢献するとともに、2020年には発明者の梅林拓氏に紫綬褒章が授与されている。

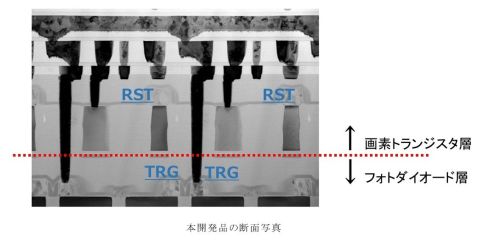

今回発表した2層トランジスタ画素積層型CMOSイメージセンサーは、これまでの画素チップの同一シリコン基板上に形成されていた各単位画素を構成するフォトダイオードと画素トランジスタを、それぞれ別の基板に分けて形成し積層する構造となっている。積層型CMOSイメージセンサーが「2階建て」とすれば、2層トランジスタ画素積層型CMOSイメージセンサーは画素チップがフォトダイオードと画素トランジスタの基板に分かれることで「3階建て」になったことになる。

「3階建て」になったことで、限られたチップ面積の中でこれまで画素トランジスタが占めていた部分をフォトダイオードにも割り当てられるようになり、従来比約2倍の飽和信号量を実現して、ダイナミックレンジを広げられる。また、転送ゲート(TRG)以外のリセットトランジスタ(RST)、セレクトトランジスタ(SEL)、アンプトランジスタ(AMP)などの画素トランジスタをフォトダイオードのない別の層に形成したことでアンプトランジスタのサイズの拡大が可能となり、夜景などの暗所撮影時に発生しやすいノイズも大幅に低減できたという。

ダイナミックレンジ拡大とノイズ低減の実現によって、逆光などの明暗差が大きいシーンでも白飛びや黒つぶれがなく、室内や夜景などの暗いシーンでもノイズの少ない高画質な撮影が可能になる。ソニーセミコンダクタソリューションズは、2層トランジスタ画素積層型CMOSイメージセンサーによって、スマートフォン撮影などのさらなる高画質化の実現に貢献していくとしている。

なお、この開発成果は、半導体や電子デバイスの国際会議「IEDM(International Electron Devices Meeting) 2021」(2021年12月11〜15日)で発表された。

関連記事

CCDやCMOSを超える裏面照射型CMOSセンサって?

CCDやCMOSを超える裏面照射型CMOSセンサって?

デジタルカメラやビデオカメラに搭載されている撮像素子「CCD」と「CMOS」の違いを基に、両者の課題を補う新技術を紹介します キヤノンの320万画素SPADセンサーが9年ぶりの快挙、独自画素構造に2つの工夫

キヤノンの320万画素SPADセンサーが9年ぶりの快挙、独自画素構造に2つの工夫

キヤノンが、暗所でも高感度に撮像が可能なSPADセンサーで、フルHD(約207万画素)を超えて「世界最高」(同社)となる320万画素を達成したと発表。従来発表の100万画素SPADセンサーから3倍以上の高画素化を実現するとともに、カラーフィルターを用いたカラー撮影も可能であり、センサーサイズも13.2×9.9mmと小型に抑えた。 ニコンが1784万画素で秒1000コマ撮像が可能な積層型CMOSイメージセンサーを開発

ニコンが1784万画素で秒1000コマ撮像が可能な積層型CMOSイメージセンサーを開発

ニコンは2021年2月17日、総画素数約1784万画素で1秒間に1000コマの撮像が可能な積層型CMOSイメージセンサーを開発したと発表した。この成果は同年2月15日から米国サンフランシスコで開催されているISSCC(国際固体素子回路会議)で発表したものである。 ソニーのイメージセンサー事業が「反転攻勢」へ、2025年度シェア60%目標を堅持

ソニーのイメージセンサー事業が「反転攻勢」へ、2025年度シェア60%目標を堅持

ソニーがCMOSセンサーをはじめとするイメージング&センシング・ソリューション(I&SS)分野の事業戦略を説明。コロナ禍前の2019年5月に発表した、2025年度におけるイメージセンサー金額シェア60%、3D ToFセンサーなどのセンシング事業の売上構成比30%という目標を堅持する方針である。 ソニーが車載LiDAR向けSPADセンサーを商品化、距離300mの検知精度は15cm

ソニーが車載LiDAR向けSPADセンサーを商品化、距離300mの検知精度は15cm

ソニーセミコンダクタソリューションズが車載LiDAR向けの積層型直接ToF(dToF)方式のSPAD距離センサー「IMX459」を商品化。10μm角の微細なSPAD画素と測距処理回路を1チップ化し、1/2.9型と小型ながら高精度かつ高速な測距を実現した。また、車載LiDAR向けのSPAD画素を用いた積層型距離センサーを商品化したのは「業界初」(同社)だという。 単露光方式でダイナミックレンジが約8倍のCMOSイメージセンサー

単露光方式でダイナミックレンジが約8倍のCMOSイメージセンサー

ソニーセミコンダクタソリューションズは、セキュリティカメラ向け1.2分の1型4K解像度CMOSイメージセンサー「IMX585」を商品化する。同社従来品と比較して、単露光方式で約8倍のダイナミックレンジを有する。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 40台超のロボットを統合管理する自律運用システムが本格稼働

- 4年目を迎えた「小さく始めるAIパビリオン」、マイコンよりMPU多めの構成に

コーナーリンク