画像認識の機械学習アルゴリズムを容易に組み込める、ザイリンクスが新開発環境:組み込み開発ニュース(1/2 ページ)

ザイリンクスは、機械学習ベースの画像認識アルゴリズムを組み込み機器で容易に活用するための開発環境「reVISIONスタック」を発表した。2017年4〜6月期の市場投入する計画。

ザイリンクスは2017年3月14日、機械学習ベースの画像認識アルゴリズムを組み込み機器で容易に活用するための開発環境「reVISIONスタック」を発表した。「Embedded World」(同年3月14〜16日、ドイツ・ニュルンベルグ)で披露した後、2017年4〜6月期に市場投入する計画。

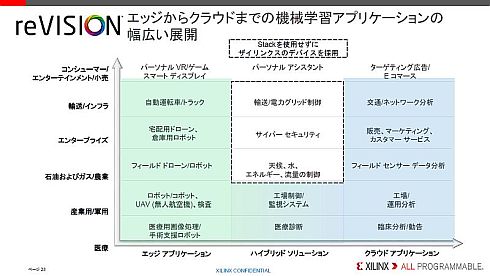

AI(人工知能)や、その基礎技術である機械学習への注目が集まっている。米国Xilinx コーポレートストラテジー&マーケティング担当シニアバイスプレジデントのスティーブ・グレイザー(Steve Glaser)氏は「機械学習を活用したアプリケーションは、エッジからクラウドに至るまで、そしてさまざまな産業/業種で活用が広がっている」と語る。

グレイザー氏は2016年12月に来日し、同社のFPGAがクラウドやデータセンターでの機械学習に適していることをアピールしている(関連記事:Xilinx、機械学習の推論に強いFPGAをアピール)。今回のreVISIONスタックは、同社FPGAを用いた機械学習の適用範囲を、クラウドやデータセンターのみならず、エッジや、エッジとクラウドを組み合わせたハイブリッド分野に広げるものだ。「機械学習を用いた画像認識のアルゴリズムやアプリケーションを、当社のFPGAに実装する上での最大の障壁は、RTL(レジスタ転送レベル)変換などの専門技術者しか扱えないHDL(ハードウェア記述言語)に関わる作業だ。reVISIONスタックを使えば、HDLを熟知しないソフトウェア技術者やシステムエンジニアでも、FPGAへの実装を容易に行える」(グレイザー氏)という。

エッジからクラウド、さまざまな産業/業種で活用が広がる機械学習。ザイリンクスはこれまでに、クラウド分野でFPGAの利用が適していることをアピールしてきた(右側の水色の網掛けの領域)。「reVISIONスタック」の投入により、エッジ分野での利用にも適しているとする(左側の薄緑色の網掛けの領域)(クリックで拡大) 出典:ザイリンクス

エッジからクラウド、さまざまな産業/業種で活用が広がる機械学習。ザイリンクスはこれまでに、クラウド分野でFPGAの利用が適していることをアピールしてきた(右側の水色の網掛けの領域)。「reVISIONスタック」の投入により、エッジ分野での利用にも適しているとする(左側の薄緑色の網掛けの領域)(クリックで拡大) 出典:ザイリンクスreVISIONスタックは、画像認識システムではクロスプラットフォームの「OpenVX」とアルゴリズムの「OpenCV」、機械学習ではライブラリ/フレームワークの「Caffe」とアルゴリズムの「GoogleNet」などに対応している。なお、機械学習のライブラリ/フレームワークについては「現時点で最も広く用いられているCaffeの他に、顧客の要望に合わせて『TensorFlow』や『Chainer』などへの対応も検討したい」(グレイザー氏)という。

開発キットとしては、ARMのアプロケーションプロセッサコアとFPGA回路を併せ持つプログラマブルSoC「Zynq」や「Zynq UltraScale+ MPSoC」を採用した「エンベデッドビジョン開発キット」を用いる。

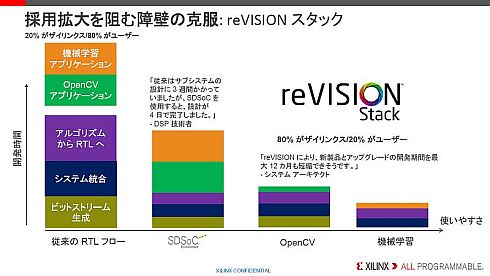

ザイリンクスは2015年3月に、Zynq向けの開発環境「SDSoC」を発表している。SDSoCは、C/C++で開発が可能なことから開発期間を大幅に短縮できることを特徴としていた。SDSoCと併せてreVISIONスタックを使えば、OpenCVや機械学習のアルゴリズム/アプリケーションの開発期間をさらに短縮できるようになる。グレイザー氏は「SDSoCより前は、ザイリンクスが開発に寄与できる比率は20%にすぎず、ユーザーが残りの80%を担当する必要があった。SDSoCに加えてreVISIONスタックを使うことでこの数字は逆転し、ザイリンクスの寄与が80%になり、ユーザーが担当するのは20%で済む。余った開発リソースは他の業務に使える」と説明する。

「SDSoC」によりZynqを用いた製品の開発期間を短縮していたが、「reVISIONスタック」を利用すれば、OpenCVや機械学習のアルゴリズム/アプリケーションの開発期間をさらに短縮できる(クリックで拡大) 出典:ザイリンクス

「SDSoC」によりZynqを用いた製品の開発期間を短縮していたが、「reVISIONスタック」を利用すれば、OpenCVや機械学習のアルゴリズム/アプリケーションの開発期間をさらに短縮できる(クリックで拡大) 出典:ザイリンクスCopyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- ソニーのフィジカルAIが卓球の一流選手に勝利、自律システム「Ace」の研究成果

コーナーリンク

ザイリンクスのスティーブ・グレイザー氏

ザイリンクスのスティーブ・グレイザー氏