第41回 IBIS AMIの基本:前田真一の最新実装技術あれこれ塾(1/3 ページ)

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第41回はIBIS AMIの基本について解説する。

本連載は「エレクトロニクス実装技術」2014年8月号の記事を転載しています。

1.IBIS AMI

「IBIS AMI」(Algorithmic Modeling Interface)はPCI Expressなど、現在規格化されている高速シリアルデータ転送方式だけでなく、将来使われるであろう技術を含め、シミュレーションに使うICの解析用モデルとして開発されました。

本来、IBIS モデルはPCI並列バスやデジタル回路の伝送線路開発用に作られたものです。そのため、モデルの対象はデジタル回路に限定し、モデルを単純化し解析時間の短縮を図っています。

しかし、信号が高速化し損失の影響が大きくなると、デジタル信号の伝送にもアナログ回路が使われるようになりました。

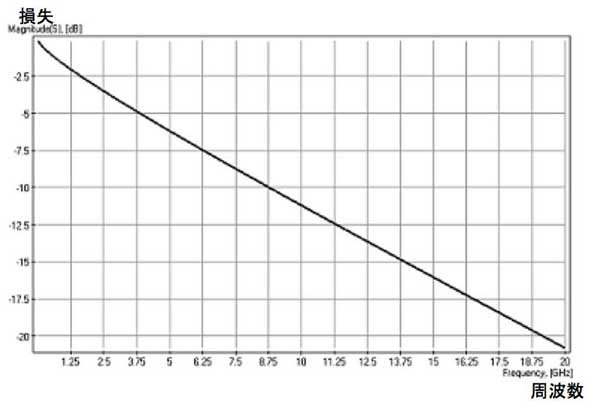

損失は周波数の高い信号ほど大きくなります(図1)。このためデジタル信号の方形波では高い周波数成分は低い周波数成分より損失がより大きくなり、信号がひずみます。

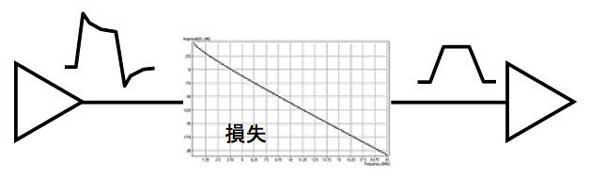

具体的には方形波の立ち上がり、立ち下がりが遅くなり、結果として、回路動作に十分なタイミングマージンが得られなくなります(図2)。

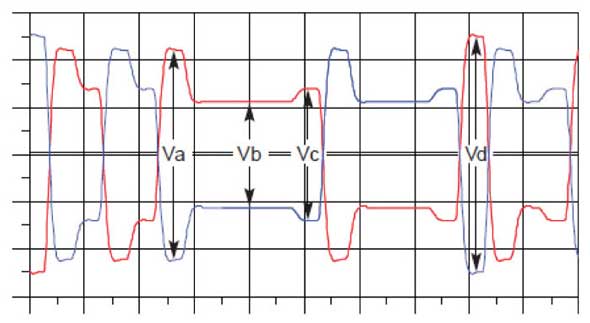

損失の影響を補正してレシーバ側で立ち上がり、立ち下がりを十分にして高速な信号を得るためには、あらかじめ高い周波数成分が大きな信号をドライバから出力すればよいことになります(図3)。

これは、PCI Express規格のプリエンファシスと呼ばれる機能です(図4)。

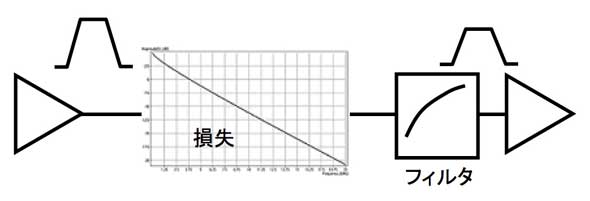

または、低い周波数成分のみを通さないようなハイパスフィルタ(図5)と呼ばれる回路を、ドライバとレシーバの間に挿入する方法もあります。

このフィルタは、ドライバの直後、レシーバの直前、伝送線路の途中、いずれにでも挿入できます。

ドライバの出力を周波数成分によって変化させるにしても、フィルタを挿入するにしても、これまでのデジタル信号をモデル化するIBISモデルでは定義できません。

IBIS AMIはこのようなアナログ的な信号や、特性の立ち上がり・立ち下がり時に定常状態で変化するような信号でもモデル化できるように開発されました。

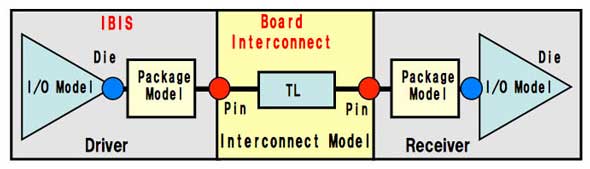

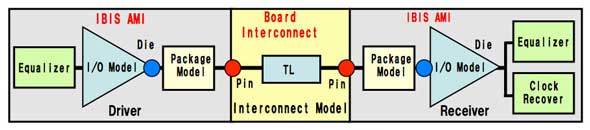

IBISモデルはICのドライバとレシーバの特性だけの定義(図6)ですが、IBIS AMIモデルはドライバ、レシーバの前後にある、特性の変更回路やフィルタ回路などの特性を含んだ特性定義になっています(図7)。

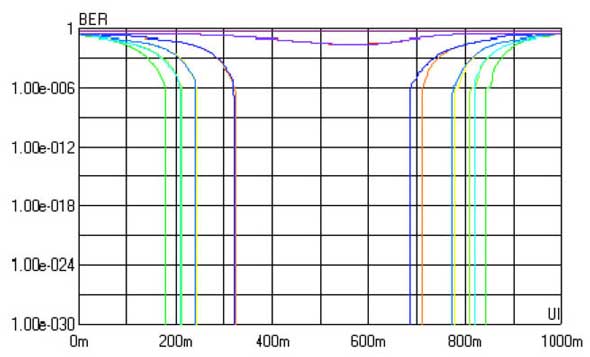

さらに、PCI Expressを始めとするシリアル転送方式で規格化されているジッタの影響によるビット・エラー・レート(Bit Error Rate:BER)の解析にも対応できるようになっています(図8)。

しかし、これまでのIBISモデルでは対応できなかった素子をモデル化するためには、単純にこれまでのIBISモデルに新しい定義を追加するだけでは対応できず、全く新しいモデルにする必要がありました。

このため、IBIS AMIモデルは、これまでのIBISモデルとは互換性がありません。

IBISモデルは最初のバージョン1から最新のバージョンまで、双方向の互換性があります。

新しいバージョンに対応していないシミュレータでも新しいバージョンで追加された機能は使えませんが、新しいバージョンのモデルを使って解析することができます。同様に、古いバージョンのIBISモデルを使っても解析は可能です。

しかし、IBIS AMIモデルはこれまでのIBISモデルとは全く異なったモデルです。バージョンに関係なく、互換性はありません。これまでのIBISモデルを使ったシミュレータではIBIS AMIモデルを使った解析は実行できません。IBIS AMIモデルはIBIS AMI用のシミュレータでなければ使えません。

また、解析の対象もIBIS AMIモデルは高速シリアルデータ転送の解析だけに使い、メモリバスや並列バス、クロック信号の解析などにはこれまでのIBISモデルを使用します。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 日本が再び世界をリードするための、“シン”モノづくりの世界

- 自動車工場で聞こえるのに、食品工場では聞こえない音〜工場の主人公は誰か

- 「自動車以外は全て好調」、四半期受注過去最高のDMG森精機が通期予想上方修正

- エンジニアリング業務を自律実行、シーメンスが産業AIを新たな段階に

- マグネットで触れるだけ、振動値を5秒で判定する回転機振動チェッカー

- 「ロボット大国」日本の逆襲、地道なモノづくりが世界を動かす交渉力に

- 猛暑に備えて

- 工場の主人公は誰なのかという問いかけ、元トヨタ生技が見た食品工場のなぜ

- ヒューマノイド中核部品がハノーバーメッセ技術賞、“脱自動車”のシェフラー開発

- 防衛事業の生産体制強化、ソナーなど水中音響センサーの新生産棟を建設

コーナーリンク

図1:損失は周波数が高いほど大きい

図1:損失は周波数が高いほど大きい 図2:損失により、方形波がひずむ

図2:損失により、方形波がひずむ 図3:高い周波数成分を大きく出力

図3:高い周波数成分を大きく出力 図4:プリエンファシス

図4:プリエンファシス 図5:低い周波数成分を小さくするフィルタを挿入

図5:低い周波数成分を小さくするフィルタを挿入 図6:IBISモデルの定義範囲

図6:IBISモデルの定義範囲 図7:IBIS AMIモデルの定義範囲

図7:IBIS AMIモデルの定義範囲 図8:ビットエラーレート(バスタブ図)

図8:ビットエラーレート(バスタブ図)