“Rapidusパーク”の先駆けとなるか、LSTCが千歳市内に光電融合技術の拠点開設:組み込み開発ニュース(2/2 ページ)

オープンイノベーション拠点に世界初の300mm角パネル対応装置群を配置

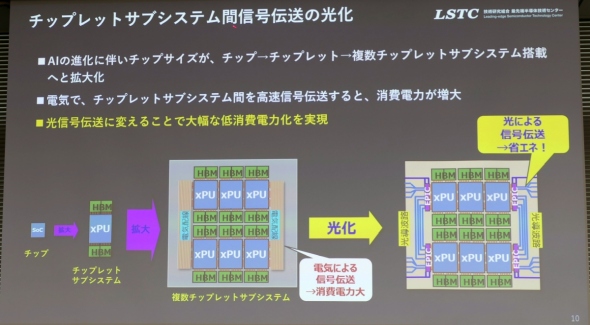

今回の開発目標で掲げる次世代光実装技術とは、AI社会の発展によるデータ通信量の劇的な増加と消費電力の増大を解決する、電気配線の限界を超える光電融合パッケージング技術のことだ。現在、半導体パッケージ内に組み込まれているチップレットや基板となるインターポーザーは全て電気配線で接続されている。今回の技術開発では、半導体パッケージ内に複数搭載されるCPUやGPUなどxPUのチップレットの間が将来的に電気配線ではなく光配線で接続されることを想定。光配線層を組み込んだ光RDL(再配線層)インターポーザーとともに、xPUに隣接して光電変換を行う光エンジンと光RDLインターポーザーを高精度に接続するハイブリッド接合技術を開発する。光RDLインターポーザー内の光配線はポリマー光導波路となっており、データ転送密度の目標は10Tbps/mm。ハイブリッド接合技術の精度は、電気配線の接続ピッチで6μmとなっている。

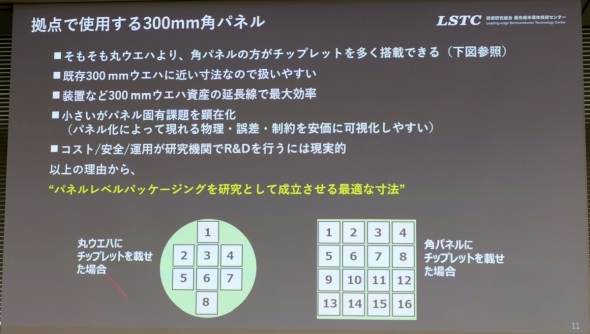

千歳科学技術大学内に整備するオープンイノベーション拠点は、広さ900m2のクリーンルームを設けて、世界初となる300mm角パネル対応の装置群を配置する予定である。300mm角パネルは直径300mmのウエハーと比べてチップレットを多数搭載できるメリットがある。一方で、Rapidusが後工程の量産に適用を検討している600mm角パネルよりも小さくなるが、既存の直径300mmウエハー対応の装置の技術を活用しやすく、パネルレベルパッケージングの研究に最適な寸法だとしている。

なお、「光電融合を加速する半導体パッケージング技術開発と先端後工程拠点形成」の期間は2026〜2030年度の5年間で、予算は総額約173億円。なお、2028年度内に開設予定のオープンイノベーション拠点への投資に約130億円を割り当てる予定だ。

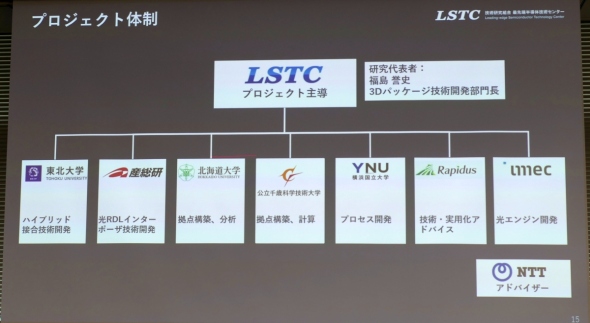

プロジェクトの体制は、LSTC主導の下で、研究代表者は東北大学 教授の福島誉史氏が務める。東北大学がハイブリッド接合技術、産業技術総合研究所が光RDLインターポーザー、北海道大学が拠点構築と分析、千歳科学技術大学が拠点構築と計算、横浜国立大学がプロセス開発を担当する。また、Rapidusは技術/実用化アドバイスを行い、ベルギーの研究機関であるimec/imec Japanが光エンジンの技術を提供する。さらに、IOWNなどで光技術の開発や実用化に注力するNTTもアドバイザーとして加わる。

関連記事

「世界で勝ち抜く意識が足りず」Rapidus東氏が語る国内半導体の過去と未来

「世界で勝ち抜く意識が足りず」Rapidus東氏が語る国内半導体の過去と未来

キャディが開催した「Manufacturing DX Summit 2023」から、同社 代表取締役の加藤勇志郎氏と東京エレクトロンで会長を務めたRapidus(ラピダス) 取締役会長の東哲郎氏による対談を抜粋して紹介する。 Rapidusの顧客獲得が進捗、60社以上と協議中で約10社にPDKをライセンスへ

Rapidusの顧客獲得が進捗、60社以上と協議中で約10社にPDKをライセンスへ

Rapidusが政府と民間企業32社からの第三者割当増資による総額約2676億円の資金調達を実施したと発表。併せて、顧客獲得の進捗状況を明らかにした。 Rapidusが半導体回路の設計期間を半減する支援ツールを投入、一部は無償提供へ

Rapidusが半導体回路の設計期間を半減する支援ツールを投入、一部は無償提供へ

Rapidusが同社のファウンドリーサービスを利用する顧客の半導体回路設計を支援するツール群を発表。7つのツールで構成されており、2026年度から順次リリースしていく予定である。このツール群を用いて半導体設計を行うことで、設計期間を50%、設計コストを30%削減できるとする。 Rapidusの2nm半導体製造拠点にIBMがMESを導入、自動化と早期立ち上げを支援

Rapidusの2nm半導体製造拠点にIBMがMESを導入、自動化と早期立ち上げを支援

日本IBMは、Rapidusの最先端半導体製造拠点「IIM-1」に半導体製造向けMES「IBM IndustryView for Semiconductor Standard」を導入した。 2nmプロセスGAAトランジスタの試作ウエハーで動作を確認

2nmプロセスGAAトランジスタの試作ウエハーで動作を確認

Rapidusは、北海道千歳市にある最先端ファウンドリ「IIM-1」で、2nm GAAトランジスタの試作ウエハーで動作を確認したと発表した。これは、同社が掲げる2027年の量産開始に向けた重要なマイルストーンとなる。 ラピダスとシーメンスが2nm世代設計基盤で戦略的協業、PDKを共同開発

ラピダスとシーメンスが2nm世代設計基盤で戦略的協業、PDKを共同開発

ラピダスは2025年6月23日、シーメンスデジタルインダストリーズソフトウェアとの間で、2nm世代以降の半導体設計/製造プロセスに関する戦略的協業を締結したと発表した。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- 40台超のロボットを統合管理する自律運用システムが本格稼働

- “Rapidusパーク”の先駆けとなるか、LSTCが千歳市内に光電融合技術の拠点開設

- 4年目を迎えた「小さく始めるAIパビリオン」、マイコンよりMPU多めの構成に

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

コーナーリンク