ラピダス半導体工場の現状と今後、パイロットライン立ち上げ開始も「まだ一合目」:FAニュース(2/2 ページ)

量産までに必要な資金は約5兆円、顧客は「1桁くらい」

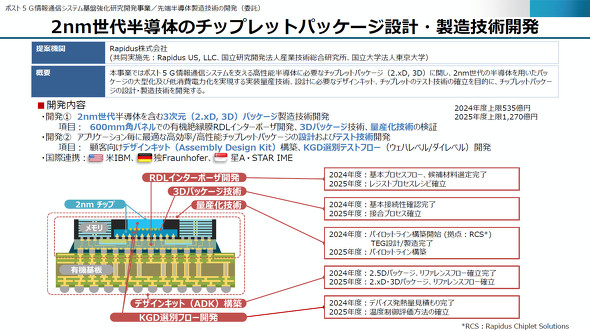

後工程に当たる、2nm世代半導体のチップレットパッケージ設計・製造技術開発では、2nm世代の半導体を用いたパッケージの大型化および低消費電力化を実現する実装量産技術、設計に必要なデザインキット、チップレットのテスト技術の確立を目的に、チップレットパッケージの設計/製造技術を開発する。

IBMやドイツの研究機関Fraunhofer、シンガポールの研究機関A STAR IMEとの国際連携で開発を進め、既に基本プロセスフローの決定および装置の選定を完了した。セイコーエプソンの千歳事業所内(北海道千歳市)に設置した、半導体後工程の研究開発拠点「Rapidus Chiplet Solutions(RCS)」では、2024年10月から稼働の準備を行っている。2025年4月からはRCSへの製造装置の導入を開始し、量産化技術確立のためのパイロットライン構築を行う。また、RDL(Redistribution Layer)インターポーザ開発、3Dパッケージ技術、最新の後工程技術に対応したADK(Assembly Design Kit)の構築推進、品質管理手法KGD(Known Good Die)の選別フローの開発を進めていく。

「後工程に関しては、1、2年かけてパイロットラインでの検証を進めていく。それをIIMに持ってきて、本格的な量産に入るのは2027年の後半から2028年の頭になる。前工程と後工程の研究開発をIIMに持ち寄り、前工程と後工程を連携して作ることで、世界一のスピードを達成できる」(小池氏)

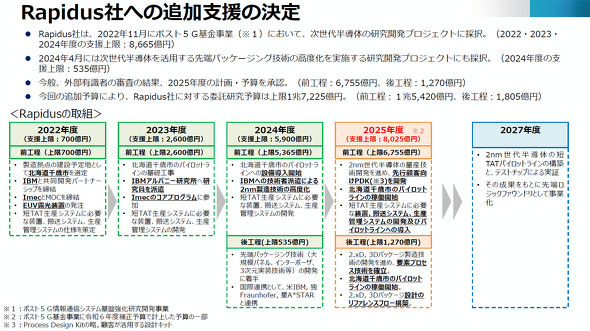

2025年度の経済産業省からの支援は最大8025億円となり、政府からの支援額は累計1兆7000億円に上る。小池氏は、研究開発段階で2兆円、量産段階で5兆円規模の資金が必要と見る。「われわれが必要としているエンジニアは1000、2000人規模となり、装置や材料など関連メーカーの従業員なども加えると、工場で働くのは数千人規模となる」(小池氏)。

民間からの資金調達に関しては、「1000億円に値するような出資をお願いしている。かなり手応えを感じている。いずれ詳細を説明できる機会が来る」(小池氏)とする。顧客については、30〜40社と「連携を強化している」(同)というが、最終的にはかなり絞られる見込みだ。

「われわれの能力と規模から見て、20〜30社というのはできない。1桁くらいになる。われわれとパートナーを組んでしっかりと進めていく企業が、2025年中には見えてくる。それによって工場の規模がある程度決まってくる。量産を開始したとしても、IIMの能力を高めていくのにそこから数年かかる」(小池氏)

関連記事

日本は、世界はどうなる? 半導体製造装置市場の見通し

日本は、世界はどうなる? 半導体製造装置市場の見通し

SEMIジャパンが行った「SEMICON Japan 2024」事前記者会見で発表された半導体製造装置市場の見通しについて説明する。 徐々にベールを脱ぐRapidus新工場、最新の状況は?

徐々にベールを脱ぐRapidus新工場、最新の状況は?

半導体サプライチェーンの国際展示会「SEMICON Japan 2024」が開幕し、オープニングセッションには官民の主要メンバーが登場した。同セッションでは、Rapidus幹部による工場建設の現状報告に注目が集まった。 Rapidusに追加で5900億円の支援、EUV露光機の導入やクリーンルームなどの稼働に

Rapidusに追加で5900億円の支援、EUV露光機の導入やクリーンルームなどの稼働に

Rapidusは、NEDOから2024年度の予算と計画の承認を受けたことを発表した。これによるRapidusへの追加支援額は5900億円になるという。 RapidusとIBMが2nm世代半導体のチップレットパッケージ技術の確立で協業

RapidusとIBMが2nm世代半導体のチップレットパッケージ技術の確立で協業

RapidusとIBMは、2nm世代半導体のチップレットパッケージ量産技術確立に向けたパートナーシップを締結した。 チップレット量産技術を開発、Rapidusが後工程研究開発機能を北海道千歳市に設置

チップレット量産技術を開発、Rapidusが後工程研究開発機能を北海道千歳市に設置

Rapidusは、北海道千歳市のセイコーエプソン 千歳事業所内にクリーンルームを構築し、半導体後工程の研究開発拠点「Rapidus Chiplet Solutions(RCS)」を開設する。 なぜ日本で2nmの先端ロジック半導体を製造しなければならないのか

なぜ日本で2nmの先端ロジック半導体を製造しなければならないのか

半導体などマイクロエレクトロニクス製造サプライチェーンの国際展示会「SEMICON Japan 2022」が2022年12月14日に開幕し、オープニングキーノートパネルとして、新たな半導体製造会社であるRapidusなども含む「半導体・デジタル産業戦略」に深く関わる主要メンバーが登壇し「グローバルリーダーを目指す産官学戦略」をテーマに、日本における半導体産業の在り方や社会変革の方向性などについて語った。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 「ロボット大国」日本の逆襲、地道なモノづくりが世界を動かす交渉力に

- 自動車工場で聞こえるのに、食品工場では聞こえない音〜工場の主人公は誰か

- ヒューマノイド中核部品がハノーバーメッセ技術賞、“脱自動車”のシェフラー開発

- ブラザー工業がパレットチェンジャー搭載シリーズの新モデル、主軸性能強化

- 複雑化/大型化するダイカスト部品の高速外観検査、NTNが新たな事業の柱模索

- 牧野フライスTOBに中止勧告、投資ファンド「大きな驚きをもって受け止め」

- 器用な指先を持つ手探りピック&プレースロボ、梱包作業の自動化で人間拡張

- データセンター向け需要に対応、大容量非常用発電システムの新工場建設へ

- ニデックがプレス機の新工場開設、生産能力倍増で工作機械とのクロスセル推進

- 滋賀本社に新工場、5面加工門形マシニングなど導入し大型部品の一貫生産強化

コーナーリンク

Rapidusの小池氏

Rapidusの小池氏