FPGAを活用した並列コンピューティングが加速、アルテラがOpenCL向けSDKを発表:2013年中に正式リリース

FPGAを並列コンピューティングの計算資源として活用するための取り組みを進めてきたアルテラは、FPGA業界初をうたう「OpenCL向けソフトウェア開発キット(SDK)」を発表した。このSDKにより、回路設計の知識のないソフトウェア開発者でもFPGAベースのアプリケーションを、迅速かつ容易に開発できるようになるという。

並列コンピューティング向けソフトウェアプログラミングのフレームワークである「OpenCL(Open Computing Language)」を、自社のFPGAに適用する研究開発プロジェクトを推進してきたFPGA大手ベンダーのAltera(アルテラ)は、2012年11月6日、FPGAの超並列アーキテクチャとOpenCLの並列プログラミングモデルを組み合わせた「OpenCL向けソフトウェア開発キット(SDK)」を発表した。「FPGA業界初のOpenCL向けSDKだ」(同社)という。

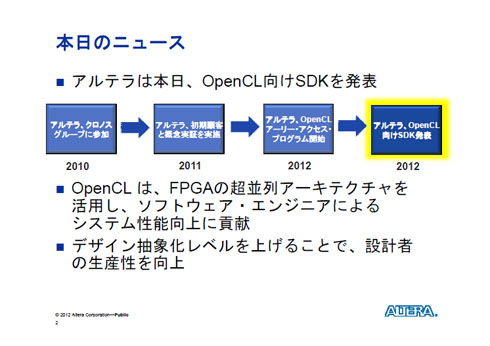

アルテラは、ホスト側のメインプロセッサのソフトウェア処理負荷をオフロードする並列コンピューティング用のハードウェアアクセラレータの選択肢の1つとして、FPGAを活用するための取り組み進めている。2010年にOpenCLの標準化を行う業界コンソーシアム「Khronos Group(クロノスグループ)」に参加。翌2011年に、初期顧客とともにコンセプトや考え方に関する実証活動を開始し、2012年から実証プロジェクトとして、OpenCLアーリーアクセスプログラムをスタートさせていた(関連記事)。

この取り組みにより寄せられた参加企業からのフィードバックを反映し、このたび、OpenCL向けSDKとして、“量産移行できる段階”に至った。現在、アーリーアクセスプログラム参加企業への提供が開始されており、「2013年中に正式リリースされる見通し」(同社)だという。

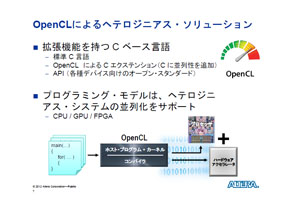

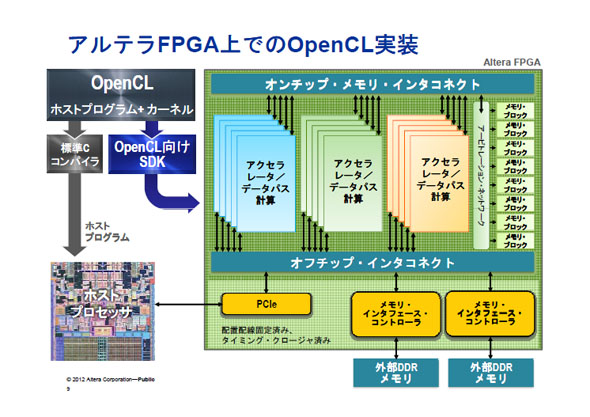

今回発表されたアルテラのOpenCL向けSDKにより、開発者は、ホスト側のメインプロセッサ(現時点ではx86アーキテクチャをサポート)で動作するプログラム(これを「ホストプログラム」と呼ぶ)と、並列コンピューティング用のハードウェアアクセラレータ、つまり、アルテラのFPGAで動作するプログラム(これを「カーネル」と呼ぶ)を、Cベースの高級言語で迅速に開発できるようになる。

C言語で記述されたホストプログラムのソースコードについては、標準的なCコンパイラによるコンパイルで実行ファイルを生成してから、ホスト側のコンピュータで実行する。一方、外部のハードウェア(FPGA)でアクセラレーションする部分(カーネルのソースコード)に関しては、アルテラのOpenCL向けSDKを使用してコンパイルする。このSDKでコンパイルすると、OpenCLカーネルファンクションのカスタムFPGAハードウェアアクセラレータへの変換、インタフェースIPの追加、インターコネクトロジックの構築、FPGAプログラミングファイルの生成が自動で行われるため、ユーザーは生成されたファイルをFPGAに書き込むだけでよい。ちなみに、このSDKには、ホストプログラム内のOpenCL APIコールにリンクするライブラリが含まれている。「これまではFPGAに精通した人しか活用することができなかったが、OpenCL向けSDKにより、回路設計の知識のないソフトウェア開発者でもFPGAを活用した並列コンピューティングが可能になった。これは非常に大きな変化だ」(同社)。

ホスト側のメインプロセッサから、外部のハードウェアアクセラレータとして機能するFPGAへ処理を引き渡す場合、PCI Expressを通じた通信によって指示が送られ、FPGA側に実装された処理が動作する。並列スレッドによるソフトウェア処理を複数コアで実行するCPUやGPGPUと異なり、FPGAの場合、カーネルファンクションについて、パイプライン並行処理の概念を用いて高度にパイプライン化したマルチスレッドの専用ハードウェア回路に変容させることができる。各パイプラインは、何度も複製し、複数のスレッドを並列に実行させることで、さらに多くの並行処理を可能にする。

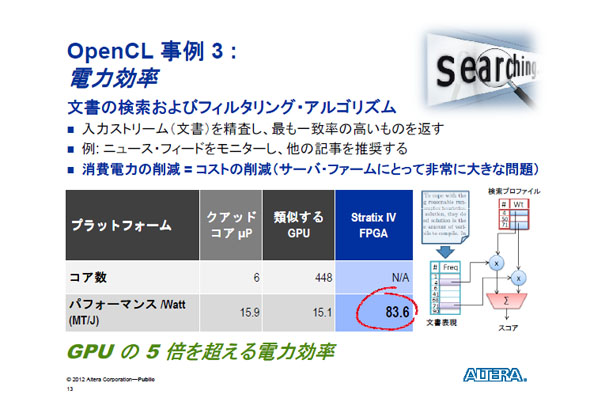

同社によると「FPGAをホスト側のメインプロセッサとともに動作させることで、CPU単体の9倍以上の性能を発揮したケースや、類似するGPUによる実装に比べて5倍以上の電力効率(1ワット当りの性能)を実現できたケースもある。また、OpenCL向けSDKにより、開発期間を数カ月短縮した事例もある」という。

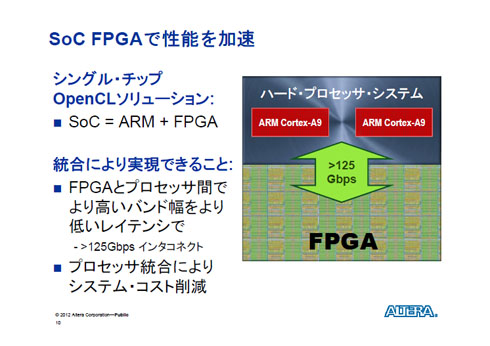

さらに、2012年12月からアーリーアクセスプログラム参加企業向けにサンプル出荷を開始するARMコア混載FPGA「SoC FPGA」も2013年中にサポートする計画である。SoC FPGAのチップ上で、ARMコア(ARM Cortex-A9のデュアル構成)をメインプロセッサとし、FPGA部を並列コンピューティング用のハードウェアアクセラレータとして利用できる。SoC FPGAの場合、プロセッサが統合されているためシステムコストが下げられるのはもちろんのこと、「メインプロセッサとFPGAがオンチップで実装されているため、接続のバンド幅は125Gbps以上になる。PCI Expressで接続する場合よりもバンド幅が飛躍的に向上し、レイテンシ(遅延)も小さくすることができる」(同社)という。

この取り組みに併せ、同社は、商業汎用ボードソリューションを提供すべく対応を進めており、現在、BittWareとNallatechの2社が提供するボードがアルテラのOpenCLをサポートしている。以降のバージョンで順次対応するボードを増やしていく計画だ。

なお、同社は11月14〜16日の3日間、パシフィコ横浜で開催される「Embedded Technology 2012/組込み総合技術展」に出展(ブース:A-21)し、FPGA向けOpenCLの性能および生産性の面における優位性を示すデモンストレーションを披露する。

関連キーワード

FPGA | アルテラ | OpenCL | SDK | 分散コンピューティング | 組み込み | Embedded | Embedded Technology | GPGPU | GPUコンピューティング | Khronos Group

関連記事

- >>「FPGA」特選コーナー

アルテラが車載分野への本格展開を宣言、年率20%以上の売上高成長を見込む

アルテラが車載分野への本格展開を宣言、年率20%以上の売上高成長を見込む

FPGAベンダー大手のアルテラが、日本市場での車載展開を本格化させる。日本アルテラ社長の日隈寛和氏は、「車載分野専任の営業、技術サポート、マーケティングなどの人員がそろい、販売代理店としっかり連携できる体制がついに整った。これからは車載分野で積極的に展開を進めていく」と宣言した。 FPGAも並列コンピューティングの選択肢に、AlteraがOpenCLの取り組み発表

FPGAも並列コンピューティングの選択肢に、AlteraがOpenCLの取り組み発表

極めて高いプロセッシング性能を求めるアプリケーションでは、CPUにGPUやDSPなどのヘテロジニアスな計算資源を組み合わせてCPUの負荷をオフロードする並列コンピューティングの適用が進んでいる。Alteraは、オフロード用資源としてFPGAを選択肢に加える取り組みについて明らかにした。- アルテラが組み込み市場への取り組みを強化、プロセッサとFPGAの融合加速へ

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 40台超のロボットを統合管理する自律運用システムが本格稼働

- “Rapidusパーク”の先駆けとなるか、LSTCが千歳市内に光電融合技術の拠点開設

- IoT向けネットワークサービスを活用しプリントシール機の安全基盤を検証

- 4年目を迎えた「小さく始めるAIパビリオン」、マイコンよりMPU多めの構成に

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

コーナーリンク

FPGA業界初をうたう「OpenCL向けSDK」を発表

FPGA業界初をうたう「OpenCL向けSDK」を発表

アルテラFPGA上でのOpenCL実装

アルテラFPGA上でのOpenCL実装

OpenCL事例からメリットを紹介。電力効率

OpenCL事例からメリットを紹介。電力効率 SoC FPGAで性能を加速

SoC FPGAで性能を加速