激動の2011年を振り返り、FPGA業界の“新時代”を占う:FPGA Watch(8)(1/2 ページ)

28nmプロセスを用いたFPGAデバイスとそれに直接関連したIPやソリューション、そして、FPGAに統合されるプロセッサの話題を中心に、2011年のFPGA業界を振り返る。そこから見えてくる2012年の動きとは!?

前回の記事から半年近くの時間があっという間に経過してしまいました。あらためて振り返ってみると、この1年でFPGAにまつわる新しい動きがこれまで以上に大きくなってきたことを強く実感します。

今回は、昨年(2011年)1年間を振り返りながら、FPGA業界の“次の1年”を考えてみたいと思います。

2011年のFPGAにまつわる主な出来事

はじめに、FPGAに関する2011年の出来事を年表風にまとめてみました(表1)。

| 発表時期(月) | 主な出来事 |

|---|---|

| 1月 | アルテラ、28nm LPプロセスの「Arria V」と「Cyclone V」のラインアップを正式発表 |

| 2月 | ザイリンクスがAutoESL Design Technologies社を買収 |

| 3月 | ザイリンクス、「Zynq-7000」ファミリを発表 |

| 3月 | ザイリンクスの「ISE Design Suite 13」、7シリーズ FPGAへの本格対応 |

| 3月 | ザイリンクス、「Kintex-7 FPGA」の出荷を発表 |

| 3月 | アルテラ、光インタフェースを備えたFPGAの技術コンセプトを発表 |

| 4月 | アルテラ、ロジックデバイスで搭載トランジスタ数が最大となる、28nm HPプロセスの「Stratix V GX FPGA」の出荷を発表 |

| 5月 | アルテラFPGAに最適化した、MIPS32アーキテクチャのソフトコアプロセッサIP「MP32」のリリースを発表 |

| 5月 | アルテラ、「Quartus II v11.0」でシステム統合ツール「Qsys」の製品版をリリース |

| 7月 | ザイリンクス、「ISE Design Suite 13.2」を発表 |

| 8月 | アルテラ、28Gbpsトランシーバを搭載した28nm HPプロセスの「Stratix V GT FPGA」の出荷を発表 |

| 8月 | NEC、C言語ベース統合設計環境「CyberWorkBench」のFPGA専用版を販売開始 |

| 9月 | アルテラ、業界初の28nm FPGA開発キットを出荷開始 |

| 9月 | アルテラ、FPGA業界初のモデルベース浮動小数点DSP機能を発表 |

| 10月 | アルテラ、「SoC FPGA」の各ラインアップを発表 |

| 10月 | アルテラ、SoC FPGA用のソフトウェア開発向け仮想プラットフォーム「Virtual Target」をリリース |

| 10月 | ザイリンクスとケイデンス社がバーチャルプラットフォームを発表 |

| 10月 | ザイリンクス、SSI技術を用いた、世界最高容量を誇る「Virtex-7」デバイスの出荷を発表 |

| 10月 | アルテラとジェナム社、次世代100Gbpsネットワーク向け4x25Gbps ICのデモンストレーションを実施 |

| 11月 | アルテラ、Quartus II開発ソフトウェア最新版 v11.1をリリース |

| 11月 | アルテラ、OpenCLの研究プロジェクトを発表 |

| 11月 | アルテラ、28nm「Arria V FPGA」の出荷開始を発表 |

| 12月 | ザイリンクス、最初の「Zynq-7000」デバイスを出荷開始 |

| 12月 | アルテラ、業界で初めて28nm FPGAとPLX Technology社PCIe Gen3スイッチとの相互接続を確認 |

| 表1 年表:FPGAに関する2011年の出来事 | |

表1は、アルテラとザイリンクスが発表したプレスリリースから、最新の28nmプロセスを用いたFPGAデバイスと、それに直接関連したIPやソリューションの発表、およびFPGAに統合されるプロセッサの話題にフォーカスし、まとめたものです。絞り込んだ内容となっておりますが、ご覧の通り、かなり多くの新しい製品や技術が発表されたことがお分かり頂けるかと思います。さらに追加として、NECから発表されたC言語ベース開発環境「CyberWorkBench」のFPGA専用版のリリースも取り上げました。

以降、この年表(表1)に記載したニュースを踏まえ、話を進めていきたいと思います。

28nmプロセスFPGAの出荷

前回の記事でも述べたように、2000年以降のロジック半導体の製造プロセス技術をけん引しているチップメーカーは、製品(商用)レベルでは数社に絞られます。その中で、FPGAはとても重要な位置付けを担います。特にアルテラとザイリンクスの2社は飛び抜けており、最新の製造プロセスによる製品開発で切磋琢磨しています。

両社とも28nm技術で3種類の製品ファミリの展開を2010年に発表。2011年には両社ともに上位・中位の2種類の製品ファミリからデバイスの出荷を開始しました。これらの製品群は、最先端の通信や放送インフラ系、コンテンツ製作や表示装置の開発に大変重要な役割を担うものです。

今年、2012年には残る1種類の製品ファミリとして、最小のコストと消費電力を実現するFPGA製品の出荷が開始されるでしょう。それにより、各種の産業機器や私たちの生活に身近な装置の開発にも寄与することでしょう。

機能、性能、消費電力への挑戦(1):FPGAデバイス内のアプローチ

FPGAはいち早く最先端の製造プロセスを使い、かつ他のロジック系デバイスよりも1〜3世代ほど先行した技術を採用することにより、集積度(機能)、性能、消費電力、コストの弱点を補っています。そして、これら要求は年々増すばかりです。製造プロセスの微細化だけではもはや実現が困難とされるこのような市場ニーズに対し、各FPGAベンダーがそれぞれのアプローチで製品を展開しています。

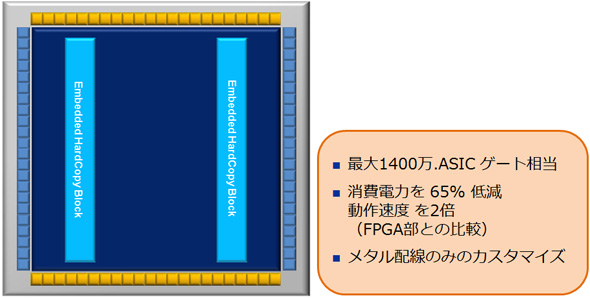

アルテラの場合は、28nmのハイエンドFPGAファミリ「Stratix V」に、Embedded HardCopy Block(以下、EHB)を搭載しています。このEHBは、ASIC技術の1つであるGate Arrayのような考え方で、メタル配線のカスタマイズを可能にした集積度の高いロジックを敷き詰めたブロックを、FPGAチップ内にあらかじめ配置して製造するものです。これにより、同面積の単一チップで、高集積化と低消費電力化を実現することができます(図1)。

一方のザイリンクスでは、28nmのハイエンドFPGAファミリ「Virtex-7」に、スタックドシリコンインターコネクト(SSIT:Stacked Silicon Interconnect Technology)を採用しました。これはマルチチップモジュール(複数のチップを基板に実装・接続してモジュール化したもの)やSIP(System In Package)と呼ばれるものに近いイメージのものです。SSITは、シリコンの基板にチップ(スライス)を実装し、各チップのI/O回路を経由することなく、シリコン基板に形成する貫通ビアを通じてチップ間の接続を実現します。これにより、接続性の制限を小さくし、性能(レイテンシ)と消費電力のペナルティを小さくするそうです。アルテラのEHBによるアプローチに比べてスケーラビリティがあり、より大規模なデバイスを供給する可能性がありそうです。

アルテラのアプローチはシングル(モノリシック)チップであり、設計ツールやユーザーの設計手法は従来通りに考えることができますが、ザイリンクスのアプローチは複数ダイにまたがる設計になるため、設計手法や検証について特別な考慮や検討が必要になるかもしれません。

ハイエンドARMプロセッサ搭載FPGA

28nmプロセスによるFPGAの製品展開において、さらに新しいものが加わりました。それは、ハイエンドのプロセッサコアをハードブロック化してFPGAとインテグレーションしたデバイスです。

ザイリンクスとアルテラがそれぞれ、ARM社のアプリケ―ションプロセッサ「Cortex-A9 MPCore」とFPGAとを統合するデバイスを発表しました。

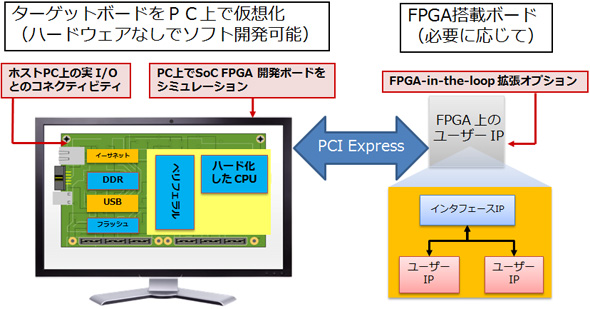

ザイリンクスは、これをExtensible Processing Platform(以下、EPP)と名付け、「Zynq」という新たな製品ファミリを追加しました。一方のアルテラは、ミッドレンジFPGAの「Arria V」と低コストFPGAの「Cyclone V」に、SoCと呼ぶ品種を拡充する形でラインアップに加えました。アルテラではこれを総称して「SoC FPGA」と呼んでいます(図2)。

さらに、アルテラからは「Virtual Target」というソフトウェア開発のための仮想プラットフォーム上でLinuxブートや仮想I/OのUSBやイーサネット接続のデモが紹介されました(図3)。また、ザイリンクスからは、一部のユーザーに向けた初期デバイスの出荷やLinuxブートのデモが発表されました。一般のユーザーに向けた製品出荷は2012年後半とアナウンスされています。

ソフトウェアとハードウェアの両方をプログラマブルにすること、そして、その両方がワンチップ化されることによる新たなアプリケーション開発と市場創出が期待されています。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 4年目を迎えた「小さく始めるAIパビリオン」、マイコンよりMPU多めの構成に

コーナーリンク

図1 Embedded HardCopy Blockのイメージ

図1 Embedded HardCopy Blockのイメージ 図2 アルテラのSoC FPGAのイメージ

図2 アルテラのSoC FPGAのイメージ 図3 SoCのソフトウェア開発:仮想プロトタイピング

図3 SoCのソフトウェア開発:仮想プロトタイピング