インテルの最新CPUアーキテクチャはより広く深く、GPUがHPCのムーンショットに:モノづくり最前線レポート(5/5 ページ)

「Ponte Vecchio」が競合との差を一気に乗り越えるムーンショットに

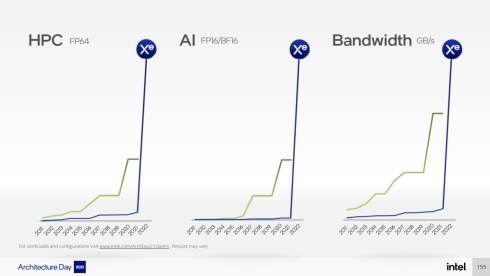

Xeは高性能ゲーミングだけでなく、「Xe HPC」としてHPC向けにも展開する。太田氏は「インテルはHPC分野で技術的に積み残してきたことが数多くあり、幾つかの仕様で競合との差が大きく開いているという現状がある。これを潔く認めつつ、競合との差を一気に乗り越える“ムーンショット”になるのがXe HPCだ」と説明する。

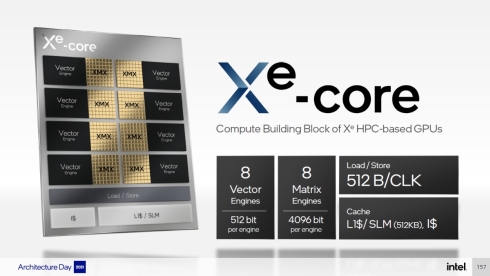

Xe HPCもコア単位はXe-coreを用いているが、Xe HPGとは構成が少し異なる。「Xe-coreは、命令セットのレベルから市場セグメントに最適化して設計できるという特性を生かした」(太田氏)。例えば、HPCで求められるFP64(倍精度浮動小数点数)に対応したり、マトリックスエンジンのビット幅をより広く取ったりしている。

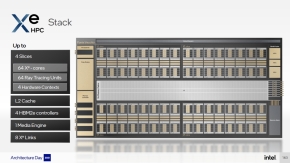

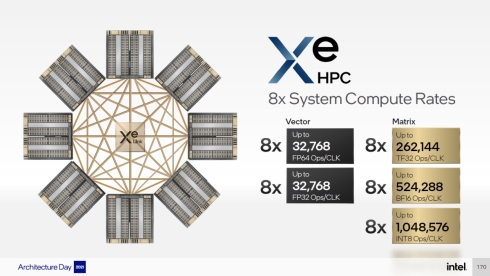

なお、Xe HPCのスライスは、それぞれ16個のXe-coreとレイトレーシングユニットなどから構成されている。さらに、このスライスを4つ束ねて高速のL2キャッシュやHBM2eコントローラー、専用ファブリックの「Xe Link」などを組み込んだスタックとなる。このスタックが、HPC向けで1個のGPUとして運用される単位になる。このスタックは、追加コンポーネントなしで最大8つまで接続可能であり、Xe Linkにより8つのスタックを1つのノードとして利用できる。

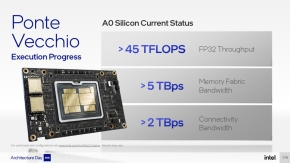

このXe HPCを製品として展開する際の形になるのが「Ponte Vecchio」である。インテルが2021年7月に発表したさまざまな半導体技術を盛り込んだPonte Vecchioは、A0シリコンと呼ぶ初期サンプルの動作を確認しており、AI処理性能はFP32で45TFlops以上、メモリファブリックの帯域幅は5TB/s以上、外部接続インタフェースの帯域幅は2TB/sを達成している。「先述した競合との差を埋めるのに十分な性能であり、まだまだやることはたくさんあるが希望が見えてきた」(太田氏)という。

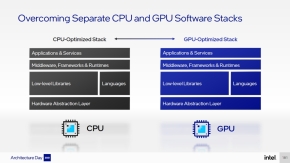

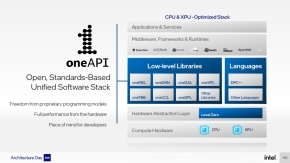

Ponte Vecchioは、1ユニットでの利用だけでなく、Xe Linksを介して複数ユニットを接続したり、Sapphire Rapidsと組み合わせたりしたサブシステムなどの構成も考えられる。しかし、CPUとGPUが共存するシステムでの課題として、CPUとGPUを用いたソフトウェア開発環境の分断がある。インテルはこの課題を解決するためのツール「oneAPI」を提唱しており、インテルの競合であるArmのCPU、NVIDIAやAMDのGPUなどにも対応するオープンなツールとなっている。

関連記事

インテルが半導体プロセスノードを再定義、2024年にはオングストローム世代へ

インテルが半導体プロセスノードを再定義、2024年にはオングストローム世代へ

インテル日本法人が、米国本社が2021年7月26日(現地時間)にオンライン配信したWebキャスト「Intel Accelerated」で発表した先端半導体製造プロセスやパッケージング技術について説明した。 新CEOの「IDM 2.0」がインテルを戒めから解き放つ、ファウンドリー事業にも本腰

新CEOの「IDM 2.0」がインテルを戒めから解き放つ、ファウンドリー事業にも本腰

インテルが、7nmプロセスの進捗状況や、ファウンドリー事業の立ち上げ、工場の建設計画などについて発表。2021年2月に新CEOに就任したパット・ゲルシンガー氏がグローバルWebキャストに登壇し、同社がこれまで堅持してきたIDM(垂直統合型デバイス製造)を大きく進化させる「IDM 2.0」のビジョンについて説明した。 10nm採用の第3世代「Xeon SP」はエッジでも展開、AI性能はNVIDIA「A100」の1.3倍

10nm採用の第3世代「Xeon SP」はエッジでも展開、AI性能はNVIDIA「A100」の1.3倍

インテル日本法人がデータセンター向けの「Xeonスケーラブル・プロセッサー(以下、Xeon SP)」の第3世代品を発表。10nmプロセスを採用することで、14nmプロセスの第2世代Xeon SPと比べて平均46%の性能向上を果たした。主な用途は、クラウド、エンタープライズ、HPC、5Gの他、IoTなどエッジでの利用も可能としている。 インテルの新プロセッサ「Tiger Lake」、トランジスタやメタル改良で高性能化

インテルの新プロセッサ「Tiger Lake」、トランジスタやメタル改良で高性能化

インテルは2020年9月3日、報道関係者向けのプレスセミナーをオンライン開催し、動作周波数の向上と消費電力の削減を同時に達成する「SuperFinプロセステクノロジー」や、新グラフィック機能などを実装した第11世代インテル Core プロセッサ ファミリーを発表した。同プロセッサの開発コード名は「Tiger Lake」である。 ディスクリートGPUまで手に入れたインテル、AI全方位戦略を強化

ディスクリートGPUまで手に入れたインテル、AI全方位戦略を強化

インテルは2019年11月27日、記者向けにAIに対する最新の取り組みについて説明会を開き、グローバルで先日発表されたGPUアーキテクチャ「Xe(エックスイー)」を含め、同社のAI向けプロセッサポートフォリオを紹介した。 目がキラッキラッのインテル新CEOゲルシンガー氏には期待せざるを得ない

目がキラッキラッのインテル新CEOゲルシンガー氏には期待せざるを得ない

いやホントに目がキラッキラッなんですよ。これが。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- イチから全部作ってみよう(31)SQLを操作して実際にデータベースを作ってみる

- “Rapidusパーク”の先駆けとなるか、LSTCが千歳市内に光電融合技術の拠点開設

- 産総研のフィジカルAIプロジェクトに迫る 10万年ギャップを超えろ!

- オープンソースの「Godot」をベースに強化した産業用リアルタイム3Dエンジン

- Arm初のCPUチップ「AGI CPU」が顧客とパートナーにもたらす悲喜こもごも

- フィジカルAI開発支援に向け「Omniverse」や「Isaac Sim」のPoC環境を無償提供

- アミューズメント機器のコイン投入量や景品出庫数をリアルタイム可視化

- 24時間連続稼働を想定したファンレスの組み込み用コントローラーを発売

- 「プリクラ」、実は高度な技術の塊だった件

- 「GoogleTest」の活用を支援するC/C++言語対応テストツール

コーナーリンク