インテルの最新CPUアーキテクチャはより広く深く、GPUがHPCのムーンショットに:モノづくり最前線レポート(3/5 ページ)

「Sapphire Rapids」はマルチタイルデザインへ

データセンター向けCPUのSapphire Rapidsは、次世代の「Xeon SP(Scalable Processor)」に位置付けられる製品だ。Performance Coreの採用により、1ノード当たりの性能を高めるだけでなく、複数ノードを組み合わせて運用するデータセンターとしての性能向上も図るべく開発されている。

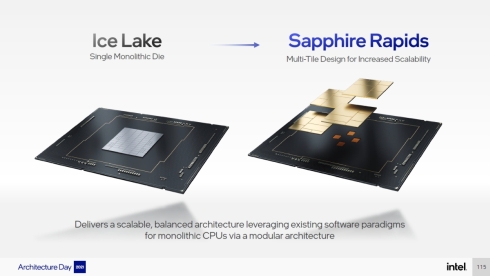

これまでのXeon SPは、1個のダイで機能を実現するモノリシックな製品だったが、Sapphire Rapidsからは複数のダイを1つのパッケージに収めて製品化する「マルチタイルデザイン」というコンセプトに変更された。「一般的にはチップレットと呼ばれている形態だが、より性能を高める仕組みを盛り込んだ『タイル』という考えた方は、チップレットを大きく超えるものだ」(土岐氏)。なお、Sapphire Rapidsでは4個のダイを「EMIB(embedded multi-die interconnect bridge)」と呼ぶ2.5次元パッケージング技術によって接続しており、「あたかも1個の大きなモノリシックなダイのようになっている」(同氏)という。

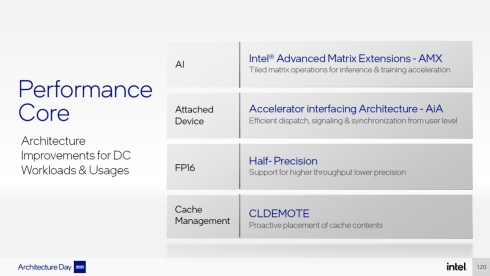

Sapphire Rapids向けのPerformance Coreでは、先述のAMXに加えて、ディスパッチや通信の信号伝送、同期などの処理をアクセラレータに移す「AiA(Accelerator interfacing Architecture)」、FP16(半精度浮動小数点演算)のサポート、キャッシュマネジメント機能の「CLDEMOTE」などが追加されている。

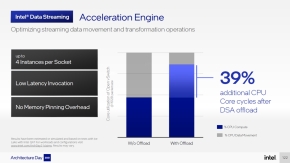

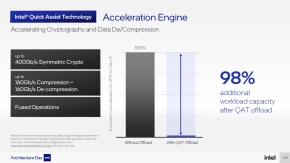

AiAで処理を移す先のアクセラレータとしては「DSA(Data Streaming accelerator)」と「QAT(Quick Assist Technology)」が用意されている。DSAは、データ転送に用いられているCPU負荷を軽減し、QSTはストレージとの間でデータをやりとりする際の暗号化や復号の処理を担う。

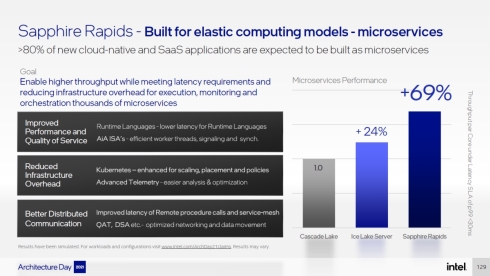

現在のデータセンターではマイクロサービスを用いて多くのアプリケーションの運用が行われている。Sapphire Rapidsは、このマイクロサービスの処理性能を向上しており、前々モデルの「Cascade Lake」比で69%増の性能向上を実現している。

「IPU」でクラウドのインフラ関連処理をオフロード

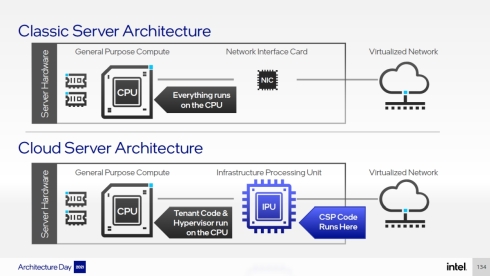

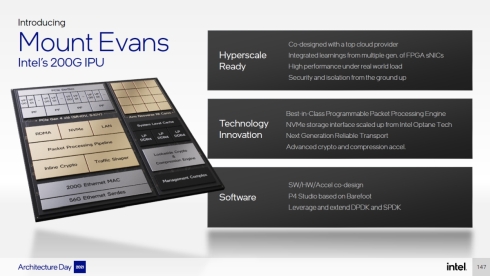

2021年6月に発表した、クラウドサービスプロバイダーのコンピューティング処理でオーバーヘッドになっているインフラ関連のタスクをオフロードするためのIPU(Infrastructure Processing Unit)の開発状況についても説明があった。

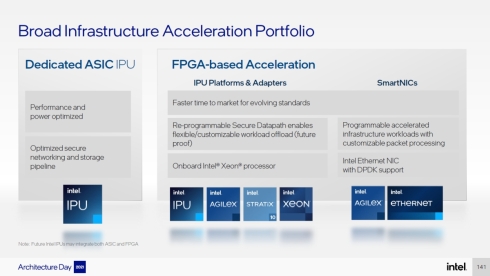

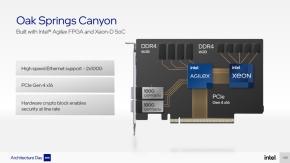

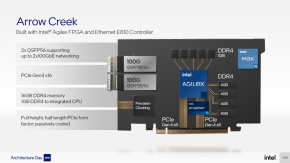

現時点では「スマートNIC」と呼ぶFPGAを搭載するカード製品が展開されているが、今後はFPGAやプロセッサの「Xeon-D」などから構成されるIPUが投入された後、将来的にはIPUに求められる機能を集積したASICを搭載する製品の計画もある。

FPGAを活用したIPUとしては、最新のFPGAである「Agilex」とXeon-Dを組み合わせた「Oak Springs Canyon」や、Agilexとイーサネットコントローラーを組み合わせたスマートNICに近い「Arrow Creek」というボード製品が予定されている。そしてASIC版となる「Mount Evans」は、クラウドサービスプロバイダーの求める仕様を盛り込んだIPUとして開発が進められている。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- イチから全部作ってみよう(31)SQLを操作して実際にデータベースを作ってみる

- “Rapidusパーク”の先駆けとなるか、LSTCが千歳市内に光電融合技術の拠点開設

- 産総研のフィジカルAIプロジェクトに迫る 10万年ギャップを超えろ!

- オープンソースの「Godot」をベースに強化した産業用リアルタイム3Dエンジン

- Arm初のCPUチップ「AGI CPU」が顧客とパートナーにもたらす悲喜こもごも

- フィジカルAI開発支援に向け「Omniverse」や「Isaac Sim」のPoC環境を無償提供

- アミューズメント機器のコイン投入量や景品出庫数をリアルタイム可視化

- 24時間連続稼働を想定したファンレスの組み込み用コントローラーを発売

- 「プリクラ」、実は高度な技術の塊だった件

- 「GoogleTest」の活用を支援するC/C++言語対応テストツール

コーナーリンク