そのアーキテクチャは要求仕様を満たす? シミュレーションで処理性能を検証:人とくるまのテクノロジー展 2017

日本シノプシスは「人とくるまのテクノロジー展2017」において、SoC(System on Chip)のマルチコア アーキテクチャの性能をシミュレーションで検討する「Platform Architect MCO」の新機能「タスクグラフジェネレーター」を紹介した。

日本シノプシスは「人とくるまのテクノロジー展2017」(2017年5月24〜26日、パシフィコ横浜)において、SoC(System on Chip)のマルチコア アーキテクチャの性能をシミュレーションで検討する「Platform Architect MCO」の新機能「タスクグラフジェネレーター」を紹介した。

ソフトウェアに適したハードウェアの性能要件や仕様を車両の開発初期段階で決められるようにするもので、半導体メーカーだけでなく自動車メーカーやティア1サプライヤーにも提案する。

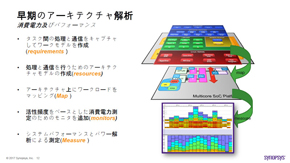

そのアーキテクチャは性能を満たせる?

車両の電子制御が複雑化することによりマルチコア アーキテクチャを前提としたソフトウェア開発が主流になっている。しかし、実際のハードウェアがなければ要求仕様を満たすかどうかを確認することが難しかった。

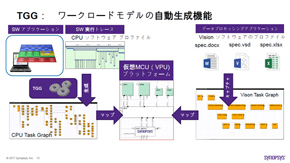

タスクグラフジェネレーターは、既存のソフトウェアからワークロードモデル(アプリケーションの負荷モデル)を生成する機能で、仮想のSoC上で想定通りのソフトウェア処理性能が出せるか検証することができる。

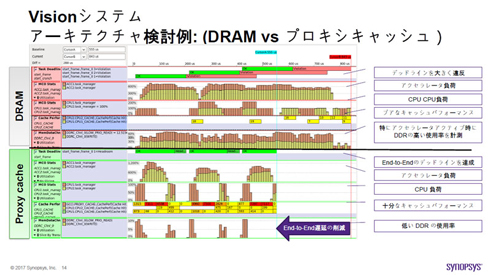

決められたタイミングに対する処理の遅延時間の他、CPUやメモリにかかる負荷、キャッシュパフォーマンスの良しあしが、実際のハードウェアなしで予測可能となる。複数のアーキテクチャをシミュレーションで比較して要求仕様を満たすものを選択できる。

タスクグラフジェネレーターでは、仮想のSoC上でソフトウェアを動作させた上で、メモリのアクセス情報や関数の依存関係を出力することができる。このため、共同開発を行う際でもソフトウェア本体の情報を共有する必要がない。例えば、自動車メーカーやティア1サプライヤー、半導体メーカーなどが共同して行う初期開発を進めやすくなるという。

関連記事

マルチコアで処理時間短縮の前にやるべきこと

マルチコアで処理時間短縮の前にやるべきこと

組み込みシステムでもマルチコアは当たり前。でもソフトウェア開発者はどのように開発を行えばいいの? マルチコアで高速化処理を実現するための手法

マルチコアで高速化処理を実現するための手法

for文やwhile文などの繰り返し処理を並列化することで、マルチコア処理の高速化、ホットスポットの高速化を図る! 【問題6】要件定義や基本設計に用いる“図”

【問題6】要件定義や基本設計に用いる“図”

今回は、要件定義や基本設計プロセスでよく利用される「ユースケース図」や「DFD」などについて解説する ソフトウェア単体から実車まで、テストって本当に大変

ソフトウェア単体から実車まで、テストって本当に大変

京子たち三立精機の制御設計チームは、モデルベース開発を活用して、ついに変速機「CVT∞」の制御ソフトウェアを完成させた。しかし、この制御ソフトウェアがきちんと動くことを確認するためにはテストを行う必要がある。ソフトウェア単体から実車を使ったものまで、さまざまなテストが待ち受けているのだ。 ルネサスからマイコンが届く前に、モデルベースでソフトウェア開発を

ルネサスからマイコンが届く前に、モデルベースでソフトウェア開発を

ルネサス エレクトロニクスは、「オートモーティブワールド2016」において、モデルベース開発環境と駆動用モーターを制御するIPを組み合わせたモデルベース開発ソリューションのデモンストレーションを実施した。ルネサスのIPによってモーター制御をリアルタイムに再現できる点を特徴としている。

Copyright © ITmedia, Inc. All Rights Reserved.

モビリティの記事ランキング

- 「EVはオワコン」なのか? 消費者の半数がガソリン車を選択、専門家の見解は

- ジヤトコのドライブユニット「GLIDE AXCEL」を搭載した電動アシスト自転車が誕生

- ヒューマノイドの“始祖”ホンダP2――「不可能」に挑んだ自立二足歩行の歩み

- トヨタが研究開発拠点「TTC-S」を公開、「走る・壊す・直す」を一気通貫で行う

- ホンダの小型EV「Super-ONE」は日常の移動に刺激を与える 2026年5月下旬に販売へ

- デンソーとロームの協業は「新たなステージ」へ、株式取得提案は取り下げ

- 欧州に迫り来るPHEV淘汰の危機

- 小型船舶でも進む操船のシステム化、環境対応も浸透――ボートショー2026レポート

- 中東情勢が国内製造業に与える減益影響じわり、日立200億円デンソー450億円

- 日本初、極超音速実験機を用いたマッハ5燃焼実験に成功

コーナーリンク