儖僱僒僗偺帺摦塣揮僔僗僥儉岦偗SoC丄ISO26262偺ASIL B偵懳墳偡傞婡擻傪幚憰丗ISO26262乮2/2 儁乕僕乯

張棟傪拞抐偣偢偵帺屓僥僗僩偡傞偵偼

丂怴奐敪偺儔儞僞僀儉僙儖僼僥僗僩婡峔偼帺屓僥僗僩傪婡擻僽儘僢僋暿偵丄偁傞偄偼1庬椶偺帺屓僥僗僩傪暋悢夞偵暘偗偰幚巤偱偒傞傛偆偵偟偨丅偙偺寢壥丄僾儘僌儔儉偺幚峴傪拞抐偡傞昁梫偑側偔丄張棟拞抐帪娫偑敪惗偟偰傕2ms埲壓偵梷偊傞偙偲偑壜擻偵側偭偨丅

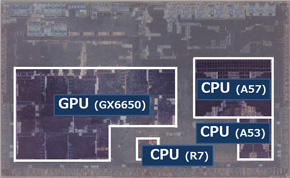

丂嬶懱揑偵偼丄CPU傗GPU偺婡擻僽儘僢僋偛偲偵帺屓僥僗僩梡偺僴乕僪僂僃傾傪搵嵹偟丄偝傜偵暋悢偺帺屓僥僗僩梡僴乕僪僂僃傾傪摑崌惂屼偡傞僐儞僩儘乕儔乕傕幚憰偟偨丅偙偺愝寁偵傛傝丄暋悢偺CPU偱峔惉偡傞CPU僋儔僗僞偺偆偪丄摿掕偺CPU偺傒偱帺屓僥僗僩傪幚峴偟偰巆傝偺CPU偱偼張棟傪宲懕偱偒傞丅傑偨丄摿掕偺CPU偱幚巤偡傞帺屓僥僗僩傪暋悢夞偵暘偗傞偙偲偱丄張棟拞抐帪娫傪嵟彫壔偡傞丅

丂僴乕僪僂僃傾偵傛傞帺屓僥僗僩偼丄僜僼僩僂僃傾偺傒偵傛傞帺屓恌抐偲斾妑偟偰僥僗僩帪娫偑抁弅偱偒傞儊儕僢僩偑偁傞丅傑偨丄榑棟夞楬傪忕挿壔偣偢偵僴乕僪僂僃傾偺屘忈傪専弌偱偒傞偨傔丄戝婯柾夞楬偱偺棙梡偵揔偟偰偄傞丅

SoC偵偁傝偑偪側屘忈傪夞旔偡傞

丂R-Car H3偼丄忣曬偺張棟懍搙傪媫寖偵崅傔偨応崌偵婲偙傞丄弖娫揑側揹埑偺崀壓偵敽偆僴乕僪僂僃傾偺屘忈傪夞旔偡傞婡擻傕旛偊傞丅偙偺揹埑崀壓偼丄SoC偺夞楬偺摦嶌廃攇悢傗妶惈壔棪偺曄壔検偑戝偒偄傎偳尠挊偵側傞丅廬棃偼揹埑儅乕僕儞傪愝偗傞愝寁偱懳墳偱偒偨偑丄16nm僾儘僙僗傪嵦梡偟偰旝嵶壔偑恑傫偩R-Car H3偱偼丄揹尮偺掅揹埑壔傗廃攇悢憹壛偵傛傞揹棳曄壔検偺奼戝偺偨傔揹埑儅乕僕儞傪愝偗傞愝寁偑擄偟偄丅

丂揹埑崀壓偵敽偆僴乕僪僂僃傾偺屘忈傪夞旔偡傞偨傔丄揹埑崀壓傪帠慜偵専抦偟偰夞楬偑妶惈壔偟偡偓側偄傛偆偵惂屼偡傞媄弍傪奐敪偟偨丅偙偺媄弍偼3偮偺婡峔偱峔惉偟偰偄傞丅

丂1偮栚偼丄崅懍摦嶌偑壜擻側揹埑専抦婡峔偩丅揹埑嵎偵傛偭偰揱斃帪娫偑曄壔偡傞壜曄抶墑夞楬偲婎弨僋儘僢僋偲偺帪娫嵎傪僨僕僞儖抣偵曄姺偡傞Time-to-Digital曄姺婡傪慻傒崌傢偣偰偄傞丅揹埑偺備傞傗偐側掅壓偵傛傞張棟偺抶墑帪娫偲丄婎弨僋儘僢僋偲偺嵎傪應傞傕偺偱丄CPU僋儘僢僋偲摨偠2GHz偱摦嶌偡傞丅

丂2偮栚偺揹埑崀壓梊應婡峔偼丄揹埑専抦婡峔偱摼偨揹埑偺忣曬傪傕偲偵4僒僀僋儖愭偺揹埑抣傪梊應偡傞丅偁傜偐偠傔愝掕偟偨鑷乮偟偒偄乯抣傪壓夞傞応崌偼丄3偮栚偺婡峔偱偁傞崅婡擻僋儘僢僋惂屼婡峔偑惂屼懳徾傊偺僋儘僢僋嫙媼傪掆巭偟丄夞楬偺夁搙側妶惈壔傪杊偖丅傑偨丄僋儘僢僋偺嫙媼偼掅偄廃攇悢偐傜彊乆偵夞暅偝偣傞偙偲偱丄僋儘僢僋偺嫙媼嵞奐偵敽偆揹埑崀壓傕杊偖丅

丂偙偺婡峔偵傛傝丄揹埑崀壓偑尨場偲側傞僴乕僪僂僃傾忈奞傪梷惂偟丄埨慡惈傪崅傔傜傟傞丅

娭楢婰帠

儖僱僒僗偺戞3悽戙乽R-Car乿偑敿帺摦塣揮傪壜擻偵偡傞

儖僱僒僗偺戞3悽戙乽R-Car乿偑敿帺摦塣揮傪壜擻偵偡傞

儖僱僒僗 僄儗僋僩儘僯僋僗偼丄幵嵹忣曬婡婍岦偗SoC偺戞3悽戙乽R-Car H3乿偺僒儞僾儖弌壸傪奐巒偟偨丅敿帺摦塣揮偵憡摉偡傞儗儀儖3偺帺摦塣揮僔僗僥儉岦偗偵丄HMI偺昤夋惈擻偲忣曬張棟惈擻傪恑壔偝偣偨丅 儖僱僒僗偑岅傞丄僋儖儅傪埨慡偵惂屼偡傞幵嵹儅僀僐儞偺乬媄弍偺巐嬿乭

儖僱僒僗偑岅傞丄僋儖儅傪埨慡偵惂屼偡傞幵嵹儅僀僐儞偺乬媄弍偺巐嬿乭

儖僱僒僗 僄儗僋僩儘僯僋僗偑丄帺摦塣揮傪帇栰偵擖傟偨塣揮巟墖僔僗僥儉岦偗偵奐敪偟偨幵嵹儅僀僐儞乽RH850/P1x-C僔儕乕僘乿偼丄摨幮偑乽幵嵹儅僀僐儞偺媄弍偺巐嬿乿偲屇傇丄僋儖儅傪埨慡偵惂屼偡傞4偮偺媄弍壽戣傪僋儕傾偟偰偄傞丅 儖僱僒僗偑RX僼傽儈儕岦偗偺婡擻埨慡搵嵹巟墖僜儕儏乕僔儑儞傪敪昞

儖僱僒僗偑RX僼傽儈儕岦偗偺婡擻埨慡搵嵹巟墖僜儕儏乕僔儑儞傪敪昞

儖僱僒僗 僄儗僋僩儘僯僋僗偼丄32價僢僩儅僀僐儞乽RX631乿乽RX63N乿傪搵嵹偡傞婡婍偵婡擻埨慡僔僗僥儉傪慻傒崬傓偨傔偺儅僯儏傾儖傗僜僼僩僂僃傾偺採嫙傪2014擭2寧偐傜奐巒偡傞丅庡偵嶻嬈婡婍偱偺婡擻埨慡懳墳傪巟墖偡傞丅 婡擻埨慡懳墳偺憱峴儌乕僞乕梡儅僀僐儞丄奜晅偗偺儗僝儖僶梡曄姺婍IC偑晄梫偵

婡擻埨慡懳墳偺憱峴儌乕僞乕梡儅僀僐儞丄奜晅偗偺儗僝儖僶梡曄姺婍IC偑晄梫偵

儖僱僒僗偺乽V850E2/PJ4-E乿偼丄帺摦幵岦偗婡擻埨慡婯奿ISO 26262偵懳墳偡傞憱峴儌乕僞乕惂屼梡儅僀僐儞偩丅廬棃偼奜晅偗偟偰偄偨儗僝儖僶梡曄姺婍IC偑晄梫偵側傞婡擻傕搵嵹偟偰偄傞丅

Copyright © ITmedia, Inc. All Rights Reserved.

儌價儕僥傿偺婰帠儔儞僉儞僌

- 僸儏乕儅僲僀僪偺乬巒慶乭儂儞僟P2乗乗乽晄壜擻乿偵挧傫偩帺棫擇懌曕峴偺曕傒

- 僕儎僩僐偺僪儔僀僽儐僯僢僩乽GLIDE AXCEL乿傪搵嵹偟偨揹摦傾僔僗僩帺揮幵偑抋惗

- 乽EV偼僆儚僐儞乿側偺偐丠丂徚旓幰偺敿悢偑僈僜儕儞幵傪慖戰丄愱栧壠偺尒夝偼

- 僩儓僞偑尋媶奐敪嫆揰乽TTC-S乿傪岞奐丄乽憱傞丒夡偡丒捈偡乿傪堦婥捠娧偱峴偆

- 婛懚慏偑帺摦塣峲慏偵両乽戞擇傎偔傟傫娵乿偺憖懬幒偵尒傞儗僩儘僼傿僢僩偺柇

- 僐儅僣偺挻戝宆帺摦塣揮僟儞僾僩儔僢僋偺摫擖戜悢偑悽奅偱弶傔偰1000戜偵摓払

- SUBARU偑暷崙EV愴棯傪尒捈偟丄尭懝寁忋偱2025擭搙偺塩嬈棙塿傪900壄墌壓曽廋惓

- 僩儓僞偼拞搶忣惃塭嬁偱6700壄墌偺尭塿尒捠偟丄壱偖椡偺嫮壔傗儘儃僥傿僋僗偱懳峈

- 僼僅乕儈儏儔E偲FIA丄怴宆揹摦儗乕僔儞僌儅僔儞乽GEN4乿偺弶憱峴傪岞奐

- 拞搶忣惃偑崙撪惢憿嬈偵梌偊傞尭塿塭嬁偠傢傝丄擔棫200壄墌僨儞僜乕450壄墌

僐乕僫乕儕儞僋