開発・デバッグ作業を楽にするFPGA開発環境:FPGA Watch(4)(2/2 ページ)

開発期間を短縮する

開発期間短縮の有効な手法の1つとして、高位な抽象度によるESL(Electronics System Level)設計メソドロジが実用化に向かっているようです。今後、ESLツールベンダ各社からFPGAをターゲットにした提案やサポートが出てくることも期待されます。ESL設計手法についての紹介は別の機会に譲り、本稿ではFPGAデバイスレベルにおける開発期間の短縮化について述べたいと思います。しかし、ESLにもFPGAデバイスレベルにも共通の重要なキーワードがあります。

それは、「モジュラー開発」です。

モジュラー開発手法は、機能を複数のモジュールとして分割し、それぞれを個別に設計、テストして、最終的に組み上げる開発の手法です。ソフトウェア開発では、当然の手法といえるでしょう。一方、ハードウェア開発の方でも、例えばASIC開発においては集積度が大きくなり、ゲートアレイからセルベースへと物理構造の変化が顕著になった15年ほど前から必須の考え方になってきたといえます。FPGAの場合、従来はASICと比較すると主に集積度や機能の複雑度が小さかったため、今日でもモジュラー開発の手法が浸透し切れているとはいえないかもしれません。

モジュラー開発の手法では、各モジュールができるだけ独立性を高くすることが、そのメリットを最大化するために有効です。つまり、モジュールの内部(実装)とインターフェイスを分離することです。これにより、開発期間の短縮に対してさまざまな恩恵を受けることができます。

- モジュールごとに独立して設計・実装できる(FPGAでは独立してコンパイルできる)

- それにより、複数の設計者がモジュールごとに同時並行的に設計・検証ができる

- 各モジュールは、全体の数分の1以下の規模であり、コンパイルやシミュレーションの時間が短い

- インターフェイスを標準化(共通化)して、設計済みモジュールをほかのデザインで再利用できる

- 変更されたモジュールだけをインクリメンタルにコンパイルし、実装することで全体の開発期間を短縮できる

- それを拡張して利用することにより、装置(機種)の上位・下位あるいは機能追加の展開が速い

ここで、開発環境・開発ソフトウェアにおける、2つの重要な要素があります。

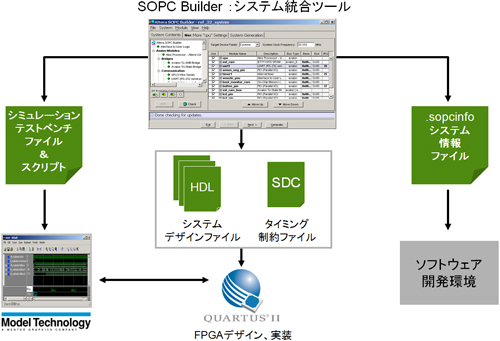

1つは“インターフェイスの共通化”です。モジュールに分けた設計を行っている設計者の方々であっても、インターフェイスを共通化するところまではなかなか実践できないのではないでしょうか。もし、個人的にそのような手法を取り入れているとしても、グループ全体、会社全体にまで展開するのはチャレンジが多いと思います。このような部分にも開発ソフトウェアツールによる支援が必要です。アルテラのQuartus IIでは、バス標準化&IP再利用のために「SOPC Builder」というソフトウェアツールを提供しています。

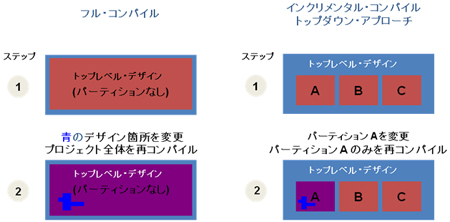

もう1つの重要な要素は、“インクリメンタルな設計フロー”です。モジュールごとに独立して設計・検証・変更を行った場合に、トップレベル(全体)ですべてを再コンパイルしなければならないと、、結局は大変長いコンパイル時間を費やさなければなりません。モジュールごとにタイミング設計が収束していても、トップレベルの実装の際にそれを維持することができなければ、全体でタイミング検証をやり直さなければなりません。このような問題を排除するためにインクリメンタル・コンパイルという機能が必要になります。

図3は「トップダウン・アプローチ」を示しています。トップレベルのデザインを進めながら、変更が必要になったモジュール(パーティション)のみを再コンパイルすることにより、コンパイル時間を短縮します。

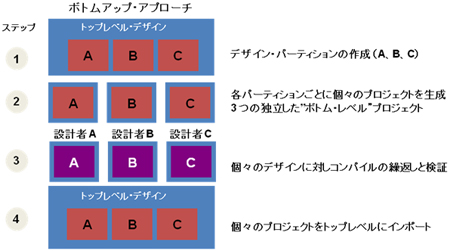

一方、図4は「ボトムアップ・アプローチ」です。最初の段階からモジュールごとに独立してデザインを進め、各モジュールのデザインが終了した後、トップレベルにインポート(統合)する設計フローです。これは「チームベース・デザイン」と呼ばれるものです。チームベースでデザインすることにより、リソースの負荷分散ができ、開発期間を短縮することが可能になります。

アルテラのQuartus IIではシンセシス(RTL合成)、配置配線の両方に対してインクリメンタル・コンパイル機能を利用できます。また、前述したトップダウン・アプローチ、ボトムアップ・アプローチの両方を取ることができます。興味のある方は、こちらで具体的な手法も紹介しています。

前回と今回の2回にわたって、現在のFPGA開発環境を紹介してきました。FPGAデザインを容易にしてくれる機能、失敗のないデザイン完了を助ける機能など、この場ではすべてを紹介し切れないほど機能がたくさんあります。本稿をきっかけに「いま」のFPGAを知っていただければ幸いです。(次回に続く)

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 4年目を迎えた「小さく始めるAIパビリオン」、マイコンよりMPU多めの構成に

コーナーリンク

図2 システム統合ツール「SOPC Builder」

図2 システム統合ツール「SOPC Builder」 図3 トップダウン・アプローチ

図3 トップダウン・アプローチ 図4 ボトムアップ・アプローチ

図4 ボトムアップ・アプローチ