FPGAにCPUを内蔵するいくつかのアプローチ:FPGA Watch(5)(1/2 ページ)

FPGAの動向をお届けする本連載。今回は、FPGAにおける“プロセッサ利用”について、特に「ソフトコアプロセッサ」のメリットを詳しく紹介する!

連載「FPGA Watch」の前回までの内容では、主にFPGAデバイスの機能・性能の発展やASICとの比較、またFPGAデバイス開発ソフトウェアの特徴的な設計ツールを紹介しました。

今回は、CPU、プロセッサにからめたFPGA業界の動向をお話ししたいと思います。

FPGAにCPUを内蔵する動き

FPGAにCPUを内蔵するアプローチは、古くから試されてきました。

例えば、プロセッサ、または言語記述によるロジック設計の教育分野でオリジナルのCPUを作成するというものから、8ビットの「8080」「8051」「Z80」「6809」など市販のCPUやマイクロコントローラとの互換性を持つIPコアの提供(IPベンダから販売)などです。また、オープンなIPコミュニティ(OpenCores.org)からも、「68000」やMIPSの「R2000」「R3000」などに互換性を持たせたCPU IPコアが提供されています。前者の場合、特に市販品の製造中止・供給中止の問題が“FPGA+CPU IPコア”を提案する動機になると考えられます。また、後者の場合は、前者と同様の理由か、あるいはソフトウェア資産の継続利用という目的が動機になると思われます。

一方、FPGAベンダ側からの直接的なアプローチも2000年ごろから現れはじめました。連載第1回「いま振り返るFPGA普及・発展の歴史」の後半でも触れましたが、アルテラ社からARM9アーキテクチャのプロセッササブシステム(ARM922T+キャッシュ+ROM/RAM+Timer+外部SDRAM I/Fなど)をハード化し、FPGA部分と併せてワンチップ化した「Excalibur」ファミリが出てきました(ちなみに、このときのFPGA部分は、同社の当時の「APEX20 FPGA」のアーキテクチャでした)。また、似たようなアプローチは、ザイリンクス社でも取られ、同社の「Virtex II Pro」から「Virtex-4」までの2世代のFPGAで「PowerPC 405」アーキテクチャのコアをハードで搭載した製品をリリースしています。

現在では、FPGA部分のアーキテクチャや半導体プロセスが古いことから、性能とコストの両面で選択肢としては考えにくい面がありますが、OSを含むソフトウェア資産の再利用(エコシステム)という観点では重要なアプローチだったと考えられます。

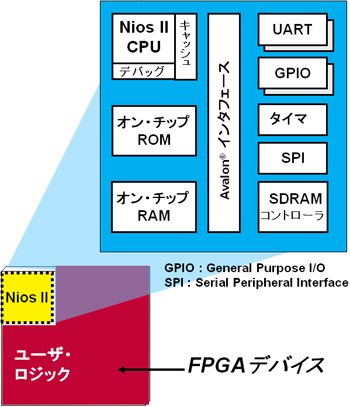

さらに、同じ時期にFPGAベンダから“正反対のアプローチ”も現れました。それは、オリジナルアーキテクチャを使い、自社のFPGAへの実装に最適化した“ソフトコア”のプロセッサです。アルテラ社の16bitの「Nios(現在は32bitのNios II)」、またザイリンクス社の「MicroBlaze」がその代表的な例です。オリジナルアーキテクチャの利点はコアそのものを低コストに利用できる点であり、ソフトコアの利点は多くのFPGAファミリに適用できること、必要なペリフェラルやI/Oを必要な数だけ搭載できること、また必要な個数を自由に内蔵できる点(つまりマルチコア)にあります。

逆に、ソフトコアがハードに比べて不利な点は、性能(動作速度)です。しかし、ターゲットとなるFPGAのアーキテクチャに合わせてコアを最適化することにより、多くのアプリケーションにおいて十分な性能を得ることも可能です(逆にいえば、FPGAに合わせて最適化していないCPUコアは面積・性能で満足を得られない場合もあります)。一例ですが、アルテラ社のNios IIを「Cyclone III」に搭載した場合、ルネサス エレクトロニクス社の「SH2」から「SH3」の性能であれば十分な動作速度を発揮できます(図1)。

クロック周波数を上げずにソフトウェア性能をブーストする3つの方法

CPUやプロセッサの性能を比較する際、動作周波数やDMIPS(Dhrystone MIPS)などの数字を指標にすることが一般的でしょう。ところが、FPGAに搭載するソフトコアプロセッサの場合は、その指標を“超えて”考えることができます。

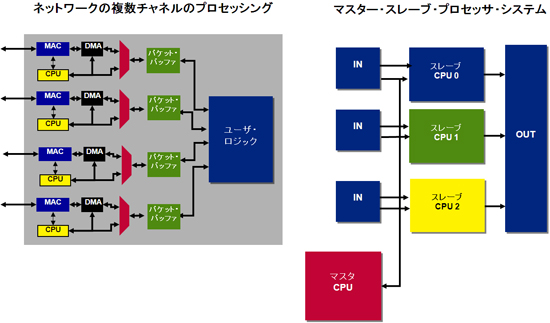

1.マルチコアによる機能分散

ソフトコアプロセッサは、FPGAのロジックリソースを限度として、何個でも搭載することができます。独立した機能ごとにソフトコアプロセッサを配置し、個別にソフトウェア処理をさせることで、個々のプロセッサの負担を小さくすることができ、結果として低い動作周波数で全体のソフトウェア処理性能を高める効果を得ることができます。

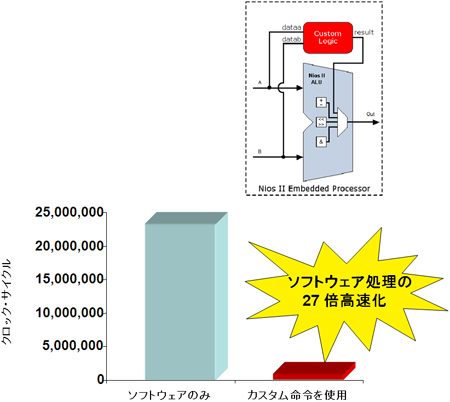

2.カスタム命令の実装

例えば、アルテラ社のソフトコアプロセッサNios IIの場合、ユーザーのカスタム命令を実装することができます。これを利用すれば、標準のままでは膨大なサイクル数を必要とする複雑な演算を高速化(サイクル数を低減)できます。CRCの計算を行う処理における、カスタム命令によるサイクル数の低減例を図3に示します。

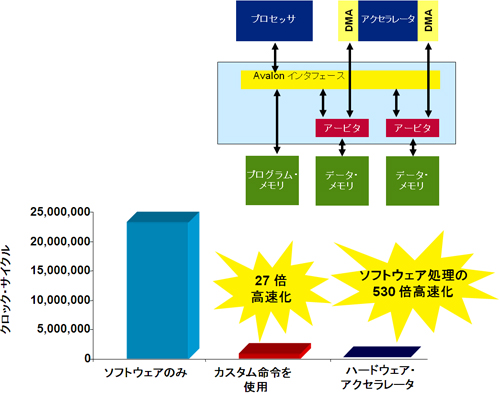

3.ハードウェアアクセラレータの採用

実行するソフトウェアの中でボトルネックになる処理がある場合、プロセッサの動作周波数に依存せずに、その部分の処理性能を向上させる有効な手法があります。それは、その処理ルーチンをハードウェア化する方法です。ハードウェアにより高速化するということで“ハードウェアアクセラレーション”と呼ばれ、そのハードウェア部分を“アクセラレータ”と呼びます。図3に示したCRC計算において、ハードウェアアクセラレータによりサイクル数を低減した例を図4に示します。

このような方法を活用できるのがFPGA+ソフトコアプロセッサの利点です。市販のプロセッサチップとの動作性能は、そのプロセッサ単体の動作周波数やMIPS(Million Instructions Per Second)値だけでは比較できなくなります。逆に、動作周波数を上げずに処理性能を高めることができるため、市販のプロセッサチップとの性能比較は、そのプロセッサ単体の動作周波数やMIPS(Million Instructions Per Second)値だけで判定できなくなります。カスタムなプロセッササブシステムを自由に柔軟に、そして容易に作成できるのです。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- 40台超のロボットを統合管理する自律運用システムが本格稼働

コーナーリンク

図1 ソフトコアプロセッサの構成例

図1 ソフトコアプロセッサの構成例 図2 機能分散型マルチプロセッシングの例

図2 機能分散型マルチプロセッシングの例 図3 ソフトウェア処理の高速化:カスタム命令

図3 ソフトウェア処理の高速化:カスタム命令 図4 ソフトウェア処理の高速化:ハードウェアアクセラレータ

図4 ソフトウェア処理の高速化:ハードウェアアクセラレータ