開発・デバッグ作業を楽にするFPGA開発環境:FPGA Watch(4)(1/2 ページ)

前回に引き続き、FPGAの開発環境について解説。FPGAは実機検証ができるだけがメリットではなく、デバッグを楽にしてくれる大きな利点もある

前回「意外とよく似ているASICとFPGAの開発フロー」では、現在のFPGAの開発手法とそれをサポートするソフトウェアや開発環境について述べました。初心者の方にとっても、FPGAのハードルは決して高くはないことを感じていただけたのではないでしょうか。また、ASIC設計経験者の方には、ASICとFPGAの設計フローは、実際にはほとんど同じであることを分かっていただけたと思います。

そして、FPGAのデバイス、IP、開発ソフトウェアによって、複雑なタイミング設計や検証を必要とする場面では、正しく動作するハード設計と実装を“ASICよりも効率よく行えること”を紹介しました。

今回も引き続き、「FPGAの開発環境」について紹介していきたいと思います。

デバッグを楽にする

「設計」という作業には「検証」が必要で、開発期間を短縮するためには双方にかかる時間・労力を低減しなければなりません。実際の設計・検証の作業には、検証して発見された「動作不具合」の原因を見つけ、見つかった原因に対策を施す、というデバッグ作業が付きものです。

カスタム・ロジック(LSI)の場合は、多くの機能がワンチップに閉じられているため、ユーザー機能を集積すればするほどデバッグ作業が難しくなりがちです。何か細工をしない限りチップ内部の状態を観測することはできません。ASICの場合には、テストピンを設けて、重要な内部状態をあらかじめ観測できるようにするとか、その観測点を多くするために「テスト・モード」を作っています。テスト・モードや内部状態を観測する手法はいろいろと考えられていますが、それ自体がさまざまな問題になっています。

具体的には、

- デバッグに必要十分な観測点をどのように決定するか

- どのようなテスト・モードにするか、どのように実装するか

- テスト・モードの設計と、テスト・モード自体の検証に要する時間

- テスト・モードの実装による回路規模の増大化

などの問題です。

仮に上記の問題をなんとかクリアしたとしても、多くのI/Oピンを取り扱うためにBGA(Ball Grid Array)パッケージを使っている場合は、外部のロジックアナライザやオシロスコープのプローブでパッケージ・ピンを触ることも至難の業になることが多いでしょう。デバッグそのものも大変な作業ですが、デバッグ方法を実装することも設計者の負担を大きくするということが容易に想像できます。

これに対して、FPGAではデバッグを楽にする手法が用意されています。メーカーによって違いがあると思いますが、ここではアルテラを例にいくつか紹介したいと思います。

- ロジックアナライザの機能をFPGA内部に組み込み、開発ソフトウェアのスクリーン上で観測する

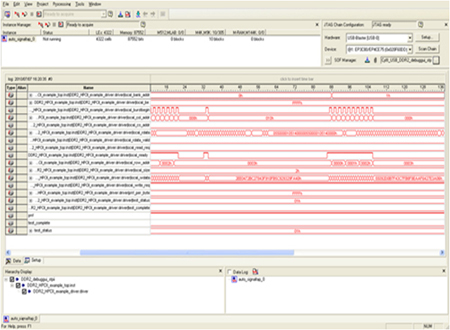

これはFPGAのユーザーロジック内にロジックアナライザ機能専用の回路を実装し、FPGA内部のあるノードの状態をサンプリングして、FPGA内部のメモリにストアしておき、FPGAが標準的に搭載しているJTAGポートを利用して外部に読み出すものです。外部に読み出した後、専用ソフトウェアでデータを表示して解析できます。アルテラでは「SignalTap II」というソフトウェアが、開発ソフトウェア「Quartus II(クオータス ツー)」に統合されています。このソフトウェアでサンプリングする内部ノードの指定やサンプリング・クロックの設定をGUIで実施できます。JTAGポート以外のI/Oピンにアクセスする必要もなく、ほかの外部機器もまったく不要であることが大きなメリットです。

この専用回路は、SignalTap II設定ファイルをイネーブルにしてコンパイルすることにより実装されます。デバッグが終わり専用回路が不要になったら、設定ファイルをディスエーブルにして再コンパイルすれば専用回路は実装されません。このためデバッグ専用回路を取り除いた最終デザインを効率よく生成できます。

この機能を活用して、テストのために指定した内部ノードに論理値を直接与え、また任意のノードを指定して結果の論理値を観測することが可能です(アルテラのツールでは「In-System Sources and Probes」)。さらに、テストのためにFPGA内部のメモリの読み出しと書き込みをJTAGポート経由で行うこともできます(アルテラのツールでは「In-System Memory Content Editor」)。興味のある方にはこちらで具体的な手法も紹介しています。

- 設計済み(配置配線済み)のFPGA内部の状態を、未使用の配線とピンを使って観測する

これもFPGA内部のノードの状態を観測する手段で、アルテラのQuartus IIでは「Signal Probe」というツールが提供している機能です。上記の方法との違いはJTAGポートを用いないことと、専用回路を実装しないことです。観測したい個所が特定しやすい場合は、専用回路を実装しないので短時間で内部の観測ができ便利でしょう。また、未使用の配線領域とI/Oピンを使用するので、デザインのタイミングに影響を与えないこともよい点です。この手法の場合は、観測用のI/Oピンに外部からプローブを当て、外部の測定器で観測するというやり方になりますので、観測の手間や装置の面では負担が増えるでしょう。

このように、FPGAには適材適所で選択できるデバッグ機能が用意されています。このような手法をASICのようなデバイスで実現することは困難だといえます。FPGAは、実機検証ができることだけがメリットではなく、“デバッグを楽にしてくれる”ということも大きなメリットなのです。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 4年目を迎えた「小さく始めるAIパビリオン」、マイコンよりMPU多めの構成に

コーナーリンク

図1 アルテラの「SignalTap II」。ロジックアナライザのような表示画面

図1 アルテラの「SignalTap II」。ロジックアナライザのような表示画面