Armのクライアント機器向け最新ソリューション「TCS23」の全貌:Arm最新動向報告(16)(1/3 ページ)

Armの最新動向について報告する本連載。今回は、2023年5月30日〜6月2日に開催された「COMPUTEX TAIPEI 2023」で発表されたクライアント機器向けの最新ソリューションである「TCS23」を構成する各IPを紹介する。

4年ぶりに海外からの取材がオープンになった2023年の「COMPUTEX TAIPEI」で、Armはクライアント機器向けのソリューションである「TCS(Total Compute Solution)」の最新版である「TCS23」と、このTCS23を構成する「Cortex-X4」「Cortex-A720/520」「Immortalis-G720」「Mali-G720/G620」「DSU-120」などの各IPを発表した。これらの内容をまとめてご紹介したい。

2021年に「Cortex-X2」などと合わせて発表された「TCS」

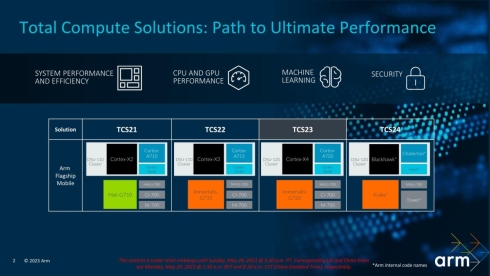

TCSは2021年の「Cortex-X2」「Cortex-A710/510」などと合わせて発表された、名前の通り“Total Solution”である。単にCPU IPだけでなく、CPU間をつなぐインターコネクトのDSU(DynamIQ Shared Unit)やGPU IP、MMU(メモリ管理ユニット)、これらをつなぐコヒーレントインターコネクトと、キャッシュコヒーレントが不要な機器をつなぐネットワークインターコネクトといった、SoCの中核をなす要素をまとめて1つのパッケージとして提供するという方式である。

2021年の発表時にロードマップも示されており(図1)、これに沿う形で2022年も製品がリリースされ、2023年も予定通りTCS23が発表されたわけだ。発表は多岐にわたるが、今回はCPUとGPUについてもう少し細かく説明したい。

「TCS23」のCPU IP

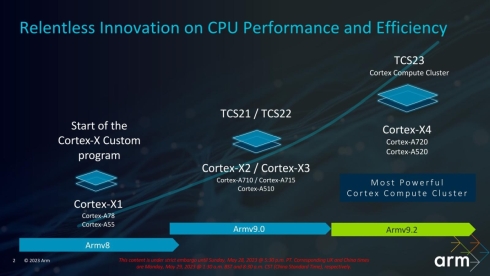

まずCPU IPであるが、さらに性能と効率を向上しただけでなく(図2)、以下のような大きな変更もあった。

- Armv9.2aの全面サポート

- 32ビットの廃止

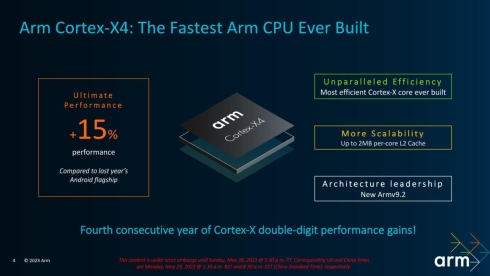

まずは性能から見てみよう。ハイエンドのCortex-X4はTCS22の「Cortex-X3」比で15%の性能改善を果たしたとする(図3)。これは猛烈な内部の強化で実現した。

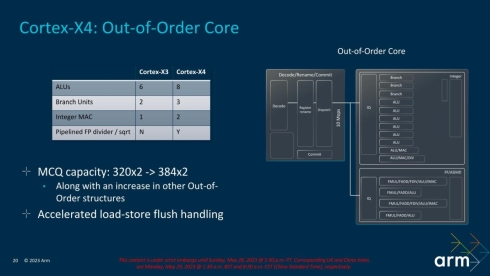

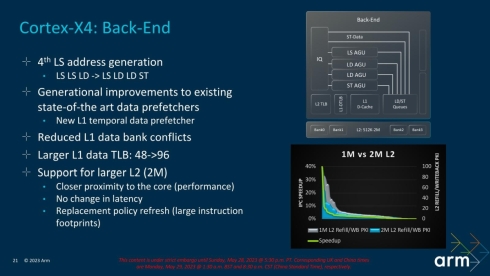

フロントエンドは10命令/cycleのデコード(図4)、バックエンドは11命令同時発行のアウトオブオーダー(図5)という代物で、これに4つのAGUが組み合わされる(図6)という、もう明らかにPCやサーバ向けと言ってもおかしくない重厚な構成である。エリアサイズはCortex-X3比で10%ほど増加しているとされるが、これは微細化(既にCortex-X3はTSMCのN3Eプロセスを用いたテストチップがテープアウトしているとのこと)でカバーできる範囲である。

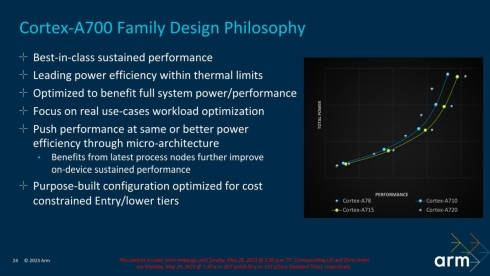

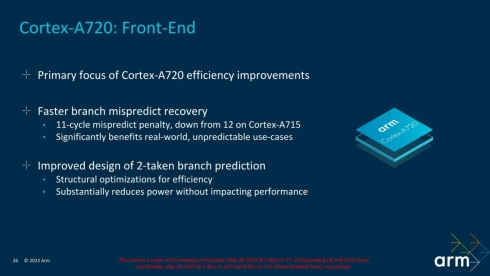

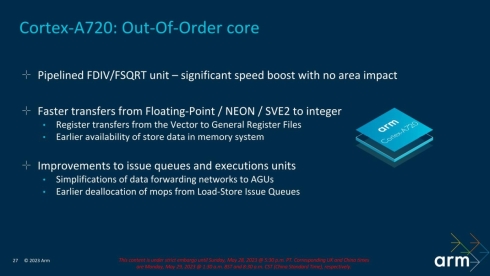

これに対してCortex-A720だが、TCS22の「Cortex-A715」比で20%程度の性能/消費電力比向上、としており絶対的な性能向上そのものはそれほど大きくない(図7)。実際パイプライン構造そのものはCortex-A715のものを継承しつつ、細かい改良で効率を改善したとしている(図8、9)。ただArmによれば、性能/消費電力比の改善は「同一プロセス、同一動作周波数で消費電力を削減」ではなく「同一プロセス、同一消費電力で動作周波数を向上」だとしているので、最大では2割程度の性能向上が得られるという。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 40台超のロボットを統合管理する自律運用システムが本格稼働

- 4年目を迎えた「小さく始めるAIパビリオン」、マイコンよりMPU多めの構成に

コーナーリンク

![図4 分岐予測も2レベルのものになったが、新たに追加したのはPerceptronベースのものか? と確認したものの詳細は教えてもらえなかった[クリックで拡大]](https://image.itmedia.co.jp/mn/articles/2307/10/sp_230710armreport16_04.jpg)