量子コンピュータの実用化を早める新アーキテクチャ、位相回転ゲート操作を高効率に:量子コンピュータ(2/2 ページ)

新アーキテクチャの開発経緯

量子ゲート方式の量子コンピュータは、現行のコンピュータと比較していくつかの領域で飛躍的に計算速度が向上すると見込まれており、さまざまな課題への適用が期待されている。しかしながら、量子コンピュータが真の性能を発揮するためには、複数の物理量子ビットから1つの論理量子ビットを形成し、量子ビットに冗長性を持たせることで、発生した量子エラーを訂正しながら計算する量子エラー訂正技術の高度化が鍵となる。

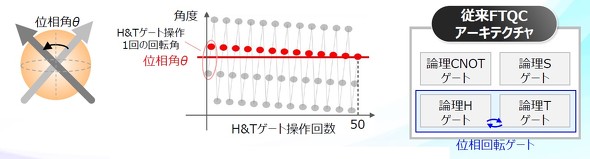

大阪大学量子情報・量子生命研究センサー 副センター長の藤井啓祐氏は、「量子エラー訂正技術のFTQCでは現在、CNOT、H、S、Tという4つの基本量子ゲートそれぞれで量子エラーを訂正し、それらの基本量子ゲートを組み合わせることで、あらゆる量子計算を量子エラーの影響なく実行可能とする方針のアーキテクチャが主流となっている」と説いた。

加えて、「しかし、量子コンピュータならではの計算を行うTゲートの量子エラー訂正には非常に多くの物理量子ビットが必要な他、量子計算に含まれる状態ベクトルの向きを回転させる操作には、論理Tゲート操作を平均して50回程度繰り返す必要がある。これに対応するためには、100万以上の物理量子ビットを備え、FTQCが可能な本格的な量子コンピュータが不可欠で、その実現には相当な年月が掛かることが予想されている」と指摘した。

そこで、大阪大学と富士通は、大阪大学の「量子情報・量子生命研究センター(Center for Quantum Information and Quantum Biology)」内に2021年10月1日に設置した「富士通量子コンピューティング共同研究部門」で、富士通が推進する「富士通スモールリサーチラボ」の一環として量子エラー訂正技術の研究開発に取り組み、新たな量子計算アーキテクチャの確立に至った。

関連記事

ソフト・ハード両方で技術革新を、富士通が量子コンピュータの共同研究開始

ソフト・ハード両方で技術革新を、富士通が量子コンピュータの共同研究開始

富士通は2020年10月13日、理化学研究所など国内外の研究機関と共同で量子コンピュータの実現に向けて開発を開始したと発表した。量子デバイスなどのハードウェアと、アルゴリズム、アプリケーションやアルゴリズムなどソフトウェア両方の領域で共同開発を進めて、量子コンピュータ実用化の障壁となる課題解決を目指す。 超伝導量子コンピュータ実用化に向け連携センター開設、理化学研究所と富士通

超伝導量子コンピュータ実用化に向け連携センター開設、理化学研究所と富士通

理研と富士通は2021年4月1日、理研の「量子コンピュータ研究センター」内に「理研RQC-富士通連携センター」を開設した。 富士通が量子コンピュータ超える新AI技術、グラフ構造データへの深層学習適用も

富士通が量子コンピュータ超える新AI技術、グラフ構造データへの深層学習適用も

富士通研究所が人工知能(AI)技術の最新成果を発表。「量子コンピュータを実用性で超える新アーキテクチャを開発」と「人やモノのつながりを表すグラフデータから新たな知見を導く新技術『Deep Tensor』を開発」の2件である。 「NISQ」による量子コンピュータ応用、「Amazon Braket」がハードルを下げる

「NISQ」による量子コンピュータ応用、「Amazon Braket」がハードルを下げる

AWSジャパンが量子コンピューティングサービス「Amazon Braket」や、量子コンピュータの技術動向について説明した。Amazon Braketは「全ての開発者、科学者の手に量子コンピューティングを」というコンセプトのフルマネージドサービスで、AWSの他のサービスと同様の手軽さで利用できるという。 グーグルの量子超越性を静観する富士通、実用性重視のAI技術で2つの「世界初」

グーグルの量子超越性を静観する富士通、実用性重視のAI技術で2つの「世界初」

富士通研究所は2019年10月25日、川崎市中原区内にある本社で会見を開き、研究開発戦略を説明するとともに新開発のAI技術を2つ発表した。これら2つのAI技術は「実用性」を大きな目的として開発されている。 RSA暗号が「ショアのアルゴリズム」に対して安全であることを証明

RSA暗号が「ショアのアルゴリズム」に対して安全であることを証明

富士通は、量子コンピュータシミュレーターを用いて、RSA暗号の安全性を定量的に評価する実験に成功した。現状では、RSA暗号が「ショアのアルゴリズム」に対して安全であることが証明された。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

素材/化学の記事ランキング

- 核融合による実用発電を目指す計画の公式パートナー制度、その狙いを考える

- 「日本にもうひとつ太陽をつくる」計画の第1弾公式パートナーが決定

- 気液間の物質移動、ガス吸収の考え方

- 100%植物原料由来のPEFフィルムを開発、高い剛性とガスバリア性を達成

- 【クイズ】国内の「錘」の減少率とは?

- 新入社員に読んで欲しい鉄鋼材料の基礎知識まとめ(Part1)

- 世界初のフッ素フリーネガ型ArF液浸レジスト、AI半導体向け先端ノードに対応

- 日本ゼオンが単層カーボンナノチューブ生産能力を数十倍へ、電池需要急増

- 千葉で油化ケミカルリサイクル設備の商業運転開始、使用済みプラを再資源化

- レゾナックがクロロプレンゴムを1kg当たり80円以上値上げ

コーナーリンク

大阪大学量子情報・量子生命研究センサー 副センター長の藤井啓祐氏

大阪大学量子情報・量子生命研究センサー 副センター長の藤井啓祐氏