56GbpsのPAM4信号に対応したトランシーバーを開発:組み込み開発ニュース

キオクシアは、新エネルギー・産業技術総合開発機構が進める「ポスト5G情報通信システム基盤強化研究開発事業」において、56GbpsのPAM4信号を送受信できるトランシーバーを開発した。

» 2022年10月18日 14時00分 公開

[MONOist]

キオクシアは2022年10月4日、NEDO(新エネルギー・産業技術総合開発機構)が進める「ポスト5G情報通信システム基盤強化研究開発事業」において、56GbpsのPAM4(4値のデータ転送方式)信号を送受信できるトランシーバーを開発したと発表した。

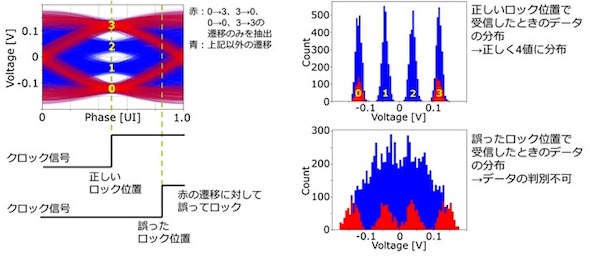

従来のCDR(クロックデータリカバリー)では、PAM4信号の特定の遷移点のみを受信データと誤認して、クロック信号が誤った位置にロックしてしまい、データを正しく受信できない状況が生じていた。

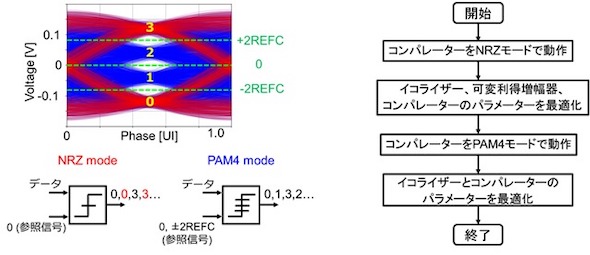

キオクシアとNEDOは、受信信号からクロック信号のロック位置を検出する際、コンパレーターをNRZ(非ゼロ復帰方式)モードで動作させることで、誤ロックを回避できることを発見した。

これを基に、コンパレーターをまずNRZモードで動作させて、クロック信号を正しい位置でロックさせた後にPAM4モードへ変更することで、PAM4信号を正しく受信できるようになった。

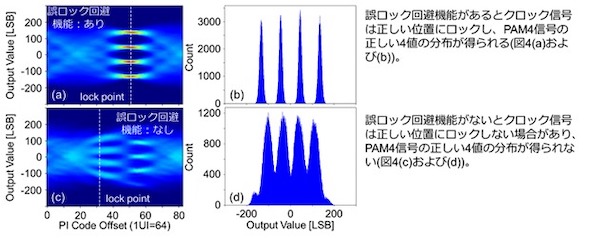

56GbpsのPAM4信号を送受信できるトランシーバーを試作し、性能評価を実施したところ、56Gbpsでの動作と誤ロック回避技術の有効性を確認できた。

キオクシアは今後、NEDOの事業として研究開発を進めているメモリディジーチェーン技術にこの成果を用いて、消費電力40W以下、容量5TB以上、帯域64Gbps以上のメモリモジュール開発を目指す。

関連記事

革新的企業トップ100初受賞のキオクシア、「単なる特許の大量取得ではない」

革新的企業トップ100初受賞のキオクシア、「単なる特許の大量取得ではない」

クラリベイト・アナリティクス・ジャパンは2022年2月24日、同社が保有する企業の特許データを基に、革新的な企業/機関を表彰する「Clarivate Top 100 グローバル・イノベーター 2022」の結果を発表した。選定の評価指標の変更などにより、日本企業の受賞社数が増加した。 キオクシアが北上工場に新棟建設、フラッシュメモリの旺盛な需要に対応

キオクシアが北上工場に新棟建設、フラッシュメモリの旺盛な需要に対応

キオクシアは2022年3月23日、3次元フラッシュメモリの生産能力増強に向け、北上工場(岩手県北上市)に2022年4月から第2製造棟(K2棟)を建設を開始すると発表した。 QLC技術採用、UFS Ver3.1準拠のPoC試作品のサンプル出荷を開始

QLC技術採用、UFS Ver3.1準拠のPoC試作品のサンプル出荷を開始

キオクシアは、モバイル機器向け組み込み式フラッシュメモリのPoC試作品のサンプル出荷を開始した。QLC技術を採用し、UFS規格に準拠しているため、ストレージの大容量化と高機能化のニーズに応える。 新製造棟建設により、3次元フラッシュメモリの生産能力を増強

新製造棟建設により、3次元フラッシュメモリの生産能力を増強

キオクシアは、四日市工場で第7製造棟の起工式を実施した。第7製造棟の建設により、3次元フラッシュメモリ「BiCS FLASH」の生産能力を増強し、最先端フラッシュメモリ製品の柔軟な生産、出荷体制を確立する。 東芝メモリが社名変更、2019年10月から「キオクシア」に

東芝メモリが社名変更、2019年10月から「キオクシア」に

東芝メモリホールディングスは2019年7月18日、2019年10月1日付で社名を「キオクシアホールディングス株式会社(英:Kioxia Holdings Corporation)」に変更すると発表した。傘下の東芝メモリを含め、同社グループ各社の社名が東芝メモリからキオクシアに置き換えられる。 東芝が全力を出せる日は来るのか、キオクシアはエルピーダと同じ道を歩むのか

東芝が全力を出せる日は来るのか、キオクシアはエルピーダと同じ道を歩むのか

「まだ本気出してない」というよりは「本気を出せる状況にない」という感じです。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

組み込み開発の記事ランキング

- 動かぬ検証機「SEIMEI」に純国産ヒューマノイド開発に向けたKyoHAの覚悟を見た

- ソフトバンクが堺にギガファクトリー、国産の燃えない水電池を2027年度に量産へ

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- ソニーのフィジカルAIが卓球の一流選手に勝利、自律システム「Ace」の研究成果

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- CPLD級のプログラマブルロジックを統合したマイコンを発表

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 安全認証対応エッジAIシステムの高度化へ向けNVIDIAとの協業を拡大

Special SitePR

コーナーリンク

あなたにおすすめの記事PR

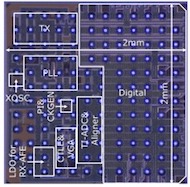

今回試作したトランシーバーのチップ写真(16nm FinFETを採用) 出所:キオクシア

今回試作したトランシーバーのチップ写真(16nm FinFETを採用) 出所:キオクシア ロック位置の違いによるデータ受信成否 出所:キオクシア

ロック位置の違いによるデータ受信成否 出所:キオクシア 誤ロックを回避するためのシーケンス 出所:キオクシア

誤ロックを回避するためのシーケンス 出所:キオクシア 誤ロック回避技術の有効性を確認した実験結果 出所:キオクシア

誤ロック回避技術の有効性を確認した実験結果 出所:キオクシア