2nm以降世代に向けた半導体プロジェクトが始動、かつての国プロとの違いとは:組み込み開発ニュース(2/2 ページ)

先端半導体製造技術コンソーシアムが共用パイロットラインを運営

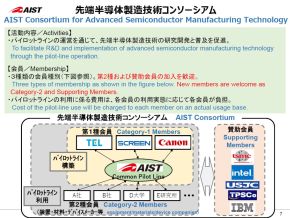

今回整備する共用パイロットラインについては、より多くの企業が利用できる体制とするため、運営組織として「先端半導体製造技術コンソーシアム」を発足させる。AISTと先述した3社が設立メンバーとして第1種会員となるものの、共用パイロットラインのユーザーとなる第2種会員や海外企業などの賛助会員の加入を積極的に進めたい考えだ。なお、現時点でSCR棟の65nmラインの利用は年間数千枚程度だが、新たな共用パイロットラインはより多くの生産枚数になるようにしていくという。また、導入装置のリストは2021年度末をめどにWebサイトで公開する予定だ。

経済産業省 商務情報政策局 情報産業課 デバイス・半導体戦略室長の荻野洋氏は「このコンソーシアムは『一緒に研究する』のではなく、パイロットラインを『一緒に使う』ことを目的としている。過去の半導体プロジェクトから学んだ結果として、この方が良いと判断した」と説明する。

なお、2nm世代以降のロジックICが対象となるものの、現在最先端の半導体製造プロセスで採用が広がるEUV(極端紫外光)露光装置は共用パイロットラインには導入されない。「予算の制限もあり導入を見送った。EUVが必要なプロセスについてはEB(電子ビーム直接描画)で代替する」(安田氏)という。

TSMCが台湾外に研究開発拠点を展開するのは初

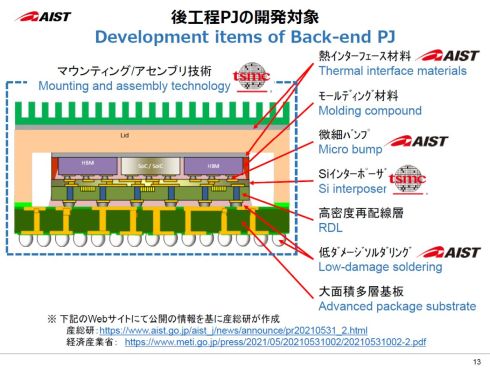

3D ICを対象とした後工程プロジェクトを実施するのは、世界最大規模の半導体ファンウンドリー企業・TSMCの日本法人である「TSMCジャパン3DIC研究開発センター株式会社」だ。なお、TSMCが台湾外に研究開発拠点を展開するのは今回が初めてのことだ。

研究開発拠点となるのは、SCR棟に隣接する高機能IoTデバイス研究棟だ。建屋は既に完成しており、現在装置や設備などの導入を進めているという。研究テーマとしては、CoWoS(Chip on Wafer on Substrate)を用いた3D ICのパッケージング技術になるとみられる。なお、詳細については、TSMCジャパン3DIC研究開発センター ディレクターのChris Chern氏が2021年12月15日のSEMICON Japanのキーノート講演に登壇して説明する予定だ。

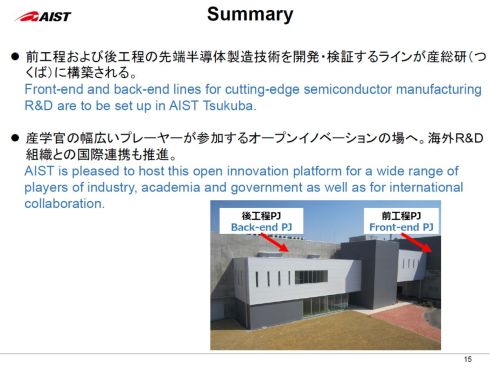

前工程プロジェクトを進める共用パイロットラインがあるSCR棟と、3D ICの技術開発を行う高機能IoTデバイス研究棟が隣接していること、共用パイロットラインを運営する先端半導体製造技術コンソーシアムにTSMCが賛助会員として参加することから、将来的には前工程と後工程を一体化した研究開発が可能になるという期待もある。「まだ具体的な話はないが、今後それぞれの研究開発を進める中でそういった検討が進むだろうと考えている」(安田氏)という。

関連記事

先端ロジック半導体のファウンドリを国内誘致へ、半導体・デジタル産業の国家戦略

先端ロジック半導体のファウンドリを国内誘致へ、半導体・デジタル産業の国家戦略

経済産業省は2021年6月4日、半導体産業やデジタル産業を国家戦略として推進する「半導体・デジタル産業戦略」を取りまとめ公開した。全ての産業の根幹にデジタル産業、半導体産業があると位置付け、先端ロジック半導体の量産化に向けたファウンドリの国内誘致推進などの戦略を紹介した。 TSMCが産総研内に評価用ライン構築、経産省の次世代半導体技術支援で

TSMCが産総研内に評価用ライン構築、経産省の次世代半導体技術支援で

経済産業省は2021年5月31日、「ポスト5G情報通信システム基盤強化研究開発事業」の「先端半導体製造技術の開発(助成)」における実施者として、「高性能コンピューティング向け実装技術」に関するTSMCなど、5件の採択を決定した。 半導体は21世紀のキーパーツ、衰退した産業基盤を国家戦略でカバーできるのか

半導体は21世紀のキーパーツ、衰退した産業基盤を国家戦略でカバーできるのか

半導体関連の国際業界団体であるSEMIジャパンは2021年6月22日、経済産業省が主催する「半導体・デジタル産業戦略検討会議」の内容を中心に同省担当者らが半導体関連の産業戦略を解説するセミナーを開催した。 TSMCが日本への工場建設を発表、2022年着工で2024年に稼働予定

TSMCが日本への工場建設を発表、2022年着工で2024年に稼働予定

台湾のファウンドリ大手であるTSMCは2021年10月14日、2021年第3四半期決算発表の場で、日本に半導体工場を建設することを発表した。 深刻化する半導体不足、納期が1年以上、価格が20〜30倍に跳ね上がるものも

深刻化する半導体不足、納期が1年以上、価格が20〜30倍に跳ね上がるものも

半導体や電子部品の通販Webサイトなどを手掛けるコアスタッフは2021年6月30日、不足が叫ばれている半導体に関する考察と、これらの状況に対する同社の取り組みについて発表した。 TSMC国内工場建設の前に、かつての日の丸半導体プロジェクトを総括してほしい

TSMC国内工場建設の前に、かつての日の丸半導体プロジェクトを総括してほしい

今度こそ失敗しないためにも、振り返りが必要だと思います

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- 40台超のロボットを統合管理する自律運用システムが本格稼働

コーナーリンク