2nm以降世代に向けた半導体プロジェクトが始動、かつての国プロとの違いとは:組み込み開発ニュース(1/2 ページ)

NEDOと経済産業省、AIST、TIAの4者が「先端半導体製造技術つくば拠点オープニングシンポジウム」を開催。「ポスト5G情報通信システム基盤強化研究開発事業」の中で進められる「先端半導体製造技術の開発」のキックオフに当たるイベントで、2nm世代以降のロジックICを対象とした前工程プロジェクトと、3D ICを対象とした後工程プロジェクトについての説明が行われた。

NEDO(新エネルギー・産業技術総合開発機構)と経済産業省、AIST(産業技術総合研究所)、TIAの4者は2021年10月28日、東京都内で「先端半導体製造技術つくば拠点オープニングシンポジウム」を開催した(オンラインでも配信)。同シンポジウムは、政府が進める「ポスト5G情報通信システム基盤強化研究開発事業」の中で進められる「先端半導体製造技術の開発」のキックオフに当たるイベントで、2nm世代以降のロジックICを対象とした前工程プロジェクトと、3D ICを対象とした後工程プロジェクトの概要やロードマップについての説明が行われた。

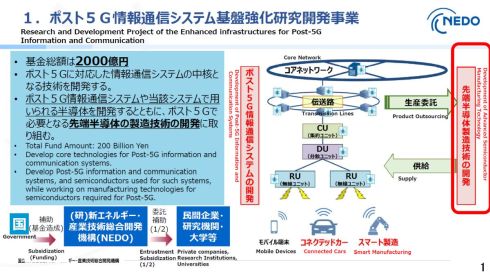

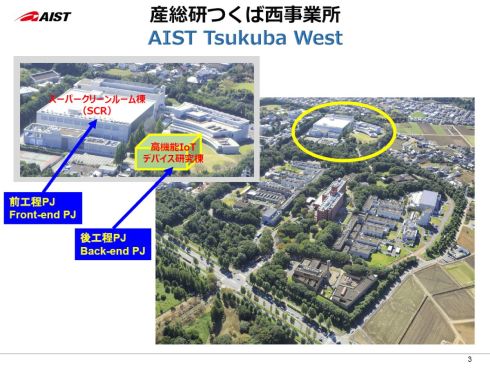

ポスト5G情報通信システム基盤強化研究開発事業の基本総額は2000億円で、政府からの委託を受けたNEDOが民間企業や研究機関、大学などへ委託する形で事業を推進している。同事業は「ポスト5G情報通信システムの開発」と「先端半導体製造技術の開発」に分かれており、このうち「先端半導体製造技術の開発」の主要拠点となるのが、TIAが管轄するSCR(スーパークリーンルーム)棟のあるAISTのつくば西事業所だ。

「先端半導体製造技術の開発」の前工程プロジェクトは、このSCR棟に2nm世代以降に対応する最先端の装置を導入して実施される。また、後工程プロジェクトのうち3D ICを対象とした技術の研究開発も、SCR棟に隣接して建設した高機能IoTデバイス研究棟で実施することになる。

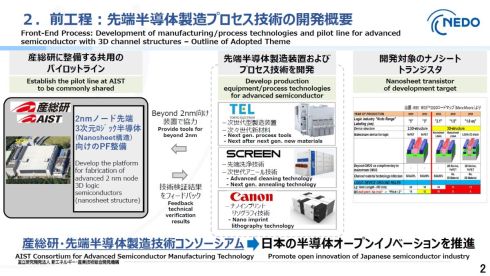

SCR棟には、2000年代に国家プロジェクトとして半導体技術開発を進めたSelete(半導体先端テクノロジーズ)の65nm世代の半導体製造ラインがある。Seleteの解散後は、AISTとTIAが半導体をはじめとするナノテクノロジーの技術開発拠点としてSCR棟を利用してきた。今回の前工程プロジェクトでは、SCR棟内に、新たに東京エレクトロンとSCREENセミコンダクターソリューションズ、キヤノンの2nm世代以降に対応する次世代装置を導入した共用パイロットラインを整備し、先端半導体製造技術を開発する。

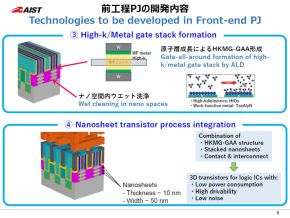

AIST エレクトロニクス・製造領域長の安田哲二氏は「2nm世代以降のロジックICのトランジスタは、現在のフィン型からナノシート型へとパラダイムシフトし、単一企業で製造技術の開発・検証を行うことは極めて困難になる。そこで、SCR棟にナノシートFETを試作できる共用パイロットラインを整備し、3社の最先端装置の開発を進めることで、ロジック半導体の製造プロセス技術を国内に確保する」と語る。

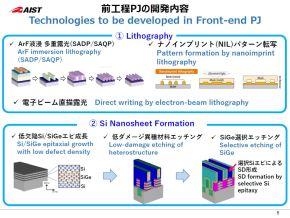

3社が担当する装置は東京エレクトロンがエッチング装置、SCREENセミコンダクターソリューションズが洗浄装置とアニーリング装置、キヤノンがナノインプリント装置になるとみられる。これらの他、ArF液浸多重露光装置、電子ビーム直描露光装置も導入する予定で、総計約20台をSCR棟に導入する。

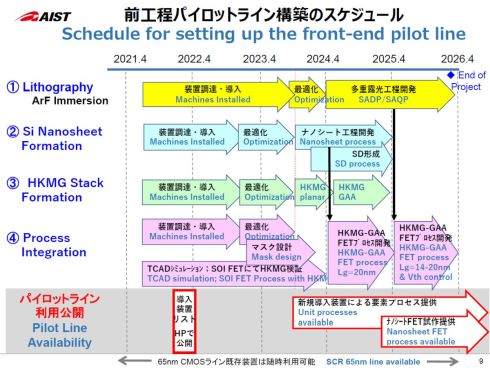

開発テーマは「リソグラフィ」「シリコンナノシート形成」「High-k/メタルゲートスタック形成」「ナノシートトランジスタプロセスインテグレーション」の4つ。現在それぞれで必要な装置調達を進めており、「リソグラフィ」は2024年度から、他の3つは2023年度半ばから共用パイロットラインを用いた開発をスタートさせる計画だ。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 40台超のロボットを統合管理する自律運用システムが本格稼働

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

コーナーリンク