ディープラーニング学習用ハードウェアの電力効率を向上させる回路技術を開発:人工知能ニュース

富士通研究所は、ディープラーニングの学習用ハードウェアの電力効率を向上させる回路技術を開発した。学習処理用データのビット幅を削減して電力効率を向上させつつも、認識性能は劣化しないため、クラウドやエッジサーバでの学習処理が可能になる。

富士通研究所は2017年4月24日、ディープラーニングの学習用ハードウェアの電力効率を向上させる回路技術を開発したと発表した。

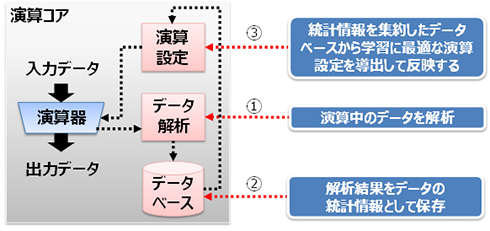

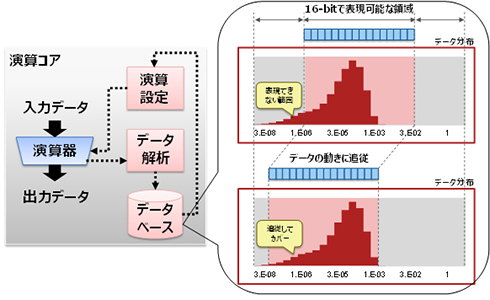

今回開発したのは、演算に用いるデータのビット幅を削減した独自の数値表現と、ディープラーニングの学習演算の特徴をもとに、演算器の動きを随時解析しながら小数点の位置を自動的に制御する演算アルゴリズムによる回路技術だ。これにより、ディープラーニングの学習過程において、演算器のビット幅や学習結果を記録するメモリのビット幅を削減でき、その結果、電力効率が向上する。

電力効率は2つの側面から向上する。1つは、浮動小数点ではなく整数で演算することによる消費電力の削減だ。また、ビット幅を32ビットから8ビットにすることで、演算器やメモリの消費電力を約75%削減できる。

同技術を実装したディープラーニング学習用ハードウェアのシミュレーションで、手書き数字認識用のLeNetとMNISTのデータセットを用いて学習した。その結果、32ビット浮動小数点演算で98.90%の認識率が、16ビットで98.89%、8ビットでも98.31%と、ほぼ同等の認識率で学習可能であることを確認した。

ディープラーニングの学習プロセスで膨大な演算処理を実行するサーバなどのハードウェアでは、利用できる電力量で処理性能の上限が決まるため、電力効率の向上が課題だった。演算に用いるビット幅を減らすなどすれば電力効率は高まるが、演算に必要な精度が不足し、ディープラーニングの認識性能が劣化してしまうことがあった。

認識性能を落とさずに、電力効率を向上できる同技術により、ディープラーニングの学習処理を、クラウドサーバだけでなくデータが生成される場所に近いエッジサーバでも適用可能になる。

関連記事

世界を変えるAI技術「ディープラーニング」が製造業にもたらすインパクト

世界を変えるAI技術「ディープラーニング」が製造業にもたらすインパクト

人工知能やディープラーニングといった言葉が注目を集めていますが、それはITの世界だけにとどまるものではなく、製造業においても導入・検討されています。製造業にとって人工知能やディープラーニングがどのようなインパクトをもたらすか、解説します。 富士通が量子コンピュータ超える新AI技術、グラフ構造データへの深層学習適用も

富士通が量子コンピュータ超える新AI技術、グラフ構造データへの深層学習適用も

富士通研究所が人工知能(AI)技術の最新成果を発表。「量子コンピュータを実用性で超える新アーキテクチャを開発」と「人やモノのつながりを表すグラフデータから新たな知見を導く新技術『Deep Tensor』を開発」の2件である。 「IoTの第2フェーズはまだ始まっていない」富士通山本正己氏

「IoTの第2フェーズはまだ始まっていない」富士通山本正己氏

10月7日まで開催されたCPS/IoT展「CEATEC JAPAN 2016」の基調講演で登壇した富士通 代表取締役会長の山本正己氏は「IoT活用の第2段階はまだ始まっていない」と述べている。 ディープラーニングの学習速度を「世界最速」に、富士通が開発

ディープラーニングの学習速度を「世界最速」に、富士通が開発

富士通研究所が複数GPUを用いて、ディープラーニングの学習速度を「世界最速」とする技術を開発した。AledNetでの評価ではGPU64台にて、単体の学習速度比で27倍という学習速度を達成した。 “実務に寄り添う”人工知能、富士通がクラウドサービスとして提供

“実務に寄り添う”人工知能、富士通がクラウドサービスとして提供

富士通は、人工知能(AI)関連技術を組み合わせてパッケージ化しクラウドサービスとして提供することを発表した。富士通でAI関連技術のみを切り出してサービスとして提供するのは初めて。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- ソニーのフィジカルAIが卓球の一流選手に勝利、自律システム「Ace」の研究成果

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 動かぬ検証機「SEIMEI」に純国産ヒューマノイド開発に向けたKyoHAの覚悟を見た

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- ソフトバンクが堺にギガファクトリー、国産の燃えない水電池を2027年度に量産へ

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

コーナーリンク

演算コアによる演算精度の向上 出典:富士通

演算コアによる演算精度の向上 出典:富士通 統計情報を用いた演算設定の最適化 出典:富士通

統計情報を用いた演算設定の最適化 出典:富士通