第51回 ウェアラブル機器とエンベデッドパッシブ:前田真一の最新実装技術あれこれ塾(3/4 ページ)

3.エンベデッドパッシブ

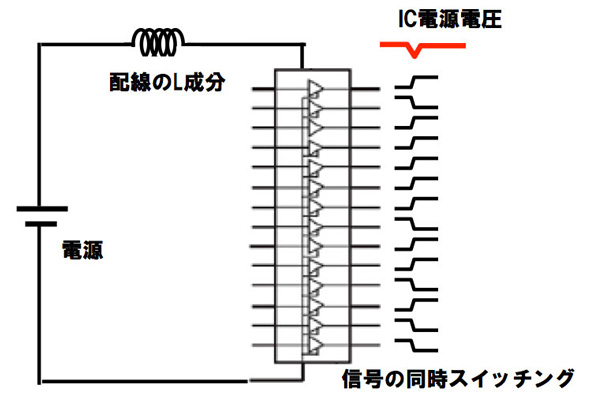

ICの消費電力が大きくなるということは、ICの消費電力の変動が大きくなるということにつながります。ICの消費電力が高速に大きく変化すると、電源供給回路からICチップ内回路の電源/グランド電流供給が変化速度に間に合わず、ICチップ内回路の電源電圧が低下します。これが同時スイッチングノイズです(図6)。

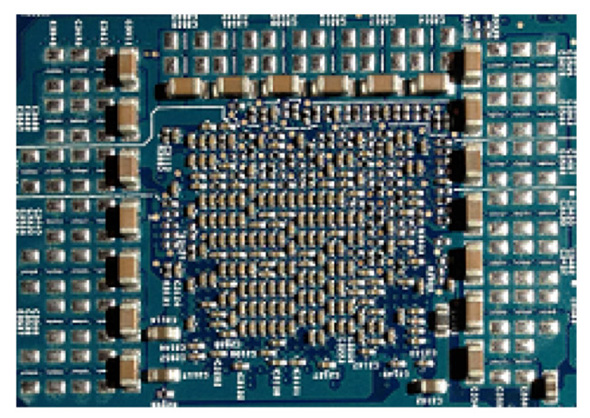

瞬間的に間に合わない電流供給を補うのがICチップの近くに配置するコンデンサ(バイパスコンデンサ)です(図7)。

バイパスコンデンサがICチップから遠くなればなるほど、コンデンサから供給する電流がICチップの電源に到達する時間が遅れます。

このため、バイパスコンデンサはできるだけICの近くに配置する必要があり、最近の高速で消費電力の大きなLSIでは、基板上だけでなくICパッケージ上にもパスコン(オン・パッケージ・コンデンサ)を配置します(図8)。

インタポーザ基板上にICチップだけでなく、コンデンサを都合のよい位置に配置できる場所の余裕があれば、オン・パッケージ・コンデンサの配置は比較的問題はありません。

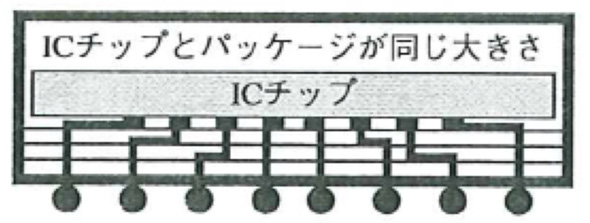

しかし、CSP(Chip Scale Package)のようにICチップ以外の部品を搭載する余裕がなかったり、ダイパッドの配置により、ダイの電源/グランドパッドから離れた場所にしかコンデンサが配置できないような場合が多くあります(図9)。

このような場合、エンベデッドパッシブ基板は同時スイッチングノイズ対策としては非常に有効な解決方法となります。

バイパスコンデンサによる有効な対策が講じられないと同時スイッチングノイズが大きくなり、回路が誤動作します。このような場合、回路の動作速度を遅くして消費電力を減らすか、同時に動作する回路ブロックの数を減らして消費電力を減らす必要があります。

LSIの消費電力が減れば、同時スイッチングノイズも減少しますが、これは、LSIの処理能力の低下になります。

インタポーザにエンベデッドパッシブ基板を使って性能向上ができるのならば、コストと性能のバランスになります。通常、高速で消費電力の大きな高機能LSIは価格も高いので、パッケージにもある程度の金額がかけられる余裕があります。パッシブ素子には、コンデンサの他にもインダクタと抵抗があります。特に抵抗は終端抵抗として、多くの抵抗を実装する必要があるので、エンベデッドパッシブ基板は、基板を小型化する上で大きな効果があるといわれています。

しかし、終端抵抗は回路や配線設計が決まらないと抵抗の値や、抵抗を挿入する位置(トポロジー)の最適値が決まりません。一般にトポロジーの決定は基板レベルのシステム設計の段階で決まるもので、パッケージインタポーザの部品設計段階では決められません。

ICチップの内部回路に大容量のLやCを組み込むことは困難なのですが、Rを作ることは容易にできます。

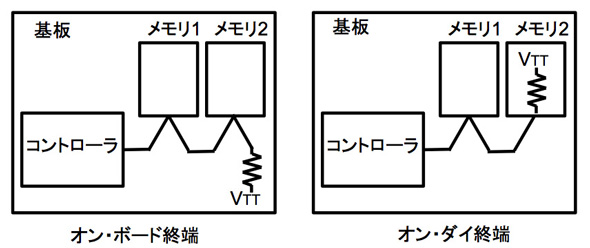

このため、DDRメモリなどではICの内部回路で終端抵抗を作るオン・ダイ・ターミネーション(ODT=On Die Termination)機能がサポートされています(図10)。

このオン・ダイ・ターミネーション機能があれば、基板やインタポーザ上に終端抵抗を配置する必要がなくなります。

このため、DDRメモリのように標準規格である程度トポロジーが決まっている場合は、オン・ダイ・ターミネーション機能が有効です。それでも、DDRメモリでも終端抵抗の値は数種類が用意されていて、基板設計後にその値を決めるようになっていて終端抵抗の最適化が図れるようになっています。

このように、抵抗のエンベデッド・パッシブ化を行うためにはシステム設計とパッケージ設計を協調して行う必要があります。

この場合でも、エンベデッドパッシブよりもオン・ダイ抵抗の方が効率が良いのは明白です。

このようにエンベデッドパッシブを終端抵抗にを使う方法はメイン基板以外には向いてはいません。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 軸受業界再編へNSKとNTNが経営統合に基本合意、両トップが語った危機感とは

- なぜオムロンは農業の“作業”ではなく“判断”の自動化を目指すのか

- 日本が再び世界をリードするための、“シン”モノづくりの世界

- 接触前に停止する協働ロボットに18kg可搬が登場、動作範囲も拡張

- 「自動車以外は全て好調」、四半期受注過去最高のDMG森精機が通期予想上方修正

- 成功率90%超でコンテナ搬送、ヒューマノイドをシーメンス工場に試験導入

- 最大26kWの超高出力化が可能、アマダが新たなファイバーレーザーマシン

- オムロンの制御機器事業が「再成長」に転換、M&Aで欧米顧客基盤を強化へ

- ヒューマノイド導入を支援するコントローラー、既存手法とVLAモデルを統合

- オムロンが電子部品事業を米国投資会社に売却、新会社名はAratasに

コーナーリンク

図6:同時スイッチングノイズ(SSN)

図6:同時スイッチングノイズ(SSN) 図7:バイパスコンデンサ

図7:バイパスコンデンサ 図8:オン・パッケージ・コンデンサ(Xbox One)

図8:オン・パッケージ・コンデンサ(Xbox One) 図9:CSP

図9:CSP 図10:オン・ダイ・ターミネーション(ODT)

図10:オン・ダイ・ターミネーション(ODT)