乽戝愗側偺偼儘僕僢僋僙儖偺悢偱偼側偄乿丄僓僀儕儞僋僗偑16nm僾儘僙僗FPGA偺徻嵶傪敪昞丗FPGA

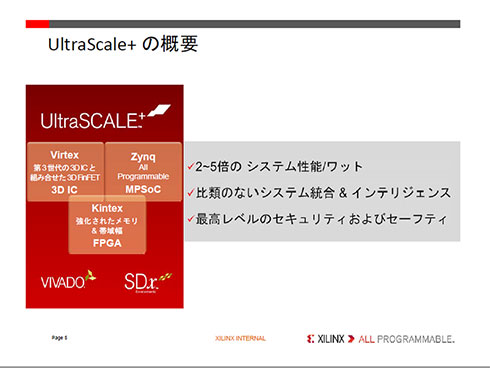

僓僀儕儞僋僗偑16nm僾儘僙僗FPGA乽UltraScale亄乿偺採嫙傪奐巒偡傞丅僴僀僄儞僪乽Virtex UltraScale亄 FPGA乿偲儈僢僪儗儞僕乽Kintex UltraScale亄 FPGA乿丄FPGA SoC乽Zynq UltraScale亄MPSoC乿傪梡堄偟丄儚僢僩摉偨傝偺僷僼僅乕儅儞僗岦忋傪慱偆丅

丂僓僀儕儞僋僗偼2015擭2寧23擔乮暷崙帪娫乯丄16nm僾儘僙僗傪嵦梡偟偨FPGA乽16nm UltraScale亄僼傽儈儕乿傪敪昞偟偨丅僴僀僄儞僪偺乽Virtex UltraScale亄 FPGA乿偲儈僢僪儗儞僕偺乽Kintex UltraScale亄 FPGA乿丄儅儖僠僾儘僙僢僔儞僌SoC乮System-On-Chip乯偺乽Zynq UltraScale亄MPSoC乿傪梡堄偟丄摨擭戞2巐敿婜偺僥乕僾傾僂僩乮愝寁姰椆乯偲戞4巐敿婜偺弌壸奐巒傪栚巜偡丅

丂UltraScale亄偼2013擭偐傜弌壸偟偰偄傞20nm僾儘僙僗FPGA乽UltraScale乿傪儀乕僗偵丄TSMC偵傛傞16nm僾儘僙僗傪揔梡偟偨FinFET偺嵦梡傗戝梕検儊儌儕偺僨僶僀僗撪憼丄偝傜偵偼僀儞僞乕僐僱僋僩嵟揔壔媄弍傗丄3D峔憿偺僩儔儞僕僗僞偱偁傞FinFET偲僔儕僐儞愙懕婎斅忋偵暋悢偺FPGA僟僀傪幚憰偡傞乽3D IC乿傪慻傒崌傢偣偨乽3D-on-3D乿媄弍側偳偺摫擖偵傛偭偰丄28nm悽戙偺惢昳偵斾傋偰1儚僢僩偁偨傝2乣5攞偺惈擻岦忋傪幚尰偟偨偲偄偆丅摨幮偵傛傟偽16nm UltraScale亄偼儚僢僩摉偨傝偺僷僼僅乕儅儞僗岦忋傪慱偆栚揑偱摫擖偝傟傞傕偺偱偁傝丄僐僗僩傪廳帇偡傞Artix僔儕乕僘偵懳偟偰偺摫擖偼寁夋偝傟偰偄側偄丅

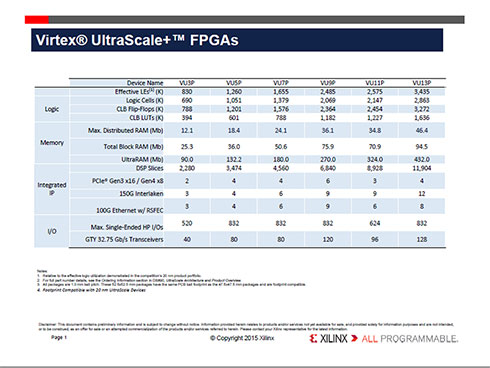

丂Virtex UltraScale亄 FPGA偼3D-on-3D媄弍偺嵦梡側偳偵傛傝儊儌儕偍傛傃懷堟暆偑嫮壔偝傟偨僴僀僄儞僪惢昳丅嵟忋埵惢昳乽VU13P乿偺儘僕僢僋僙儖悢偼286枩屄偱丄DSP僗儔僀僗偼1枩1904屄丅32.75G價僢僩/昩偺僩儔儞僔乕僶傪128屄搵嵹偟偰偍傝丄桳慄捠怣傗僱僢僩儚乕僋張棟偵揔偡傞丅

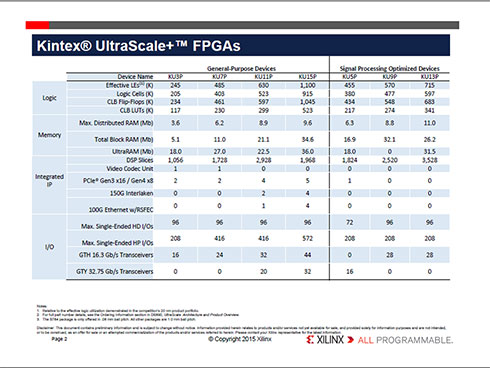

丂Kintex UltraScale亄 FPGA偼僨乕僞僙儞僞乕傗儚僀儎儗僗愝旛丄峲嬻塅拡嶻嬈傊偺嵦梡傪偵傜傫偩儈僢僪儗儞僕惢昳偱丄儘僕僢僋僙儖悢偑嵟戝915枩屄傑偱偺6昳庬傪偦傠偊偨丅DSP僗儔僀僗偼嵟戝3528屄丅捠怣懍搙偑32.75G價僢僩/昩偺僩儔儞僔乕僶傪嵟戝32屄搵嵹偟偰偄傞乮16.35G價僢僩/昩偺僩儔儞僔乕僶傕摨帪搵嵹偡傞惢昳傕偁傞乯丅

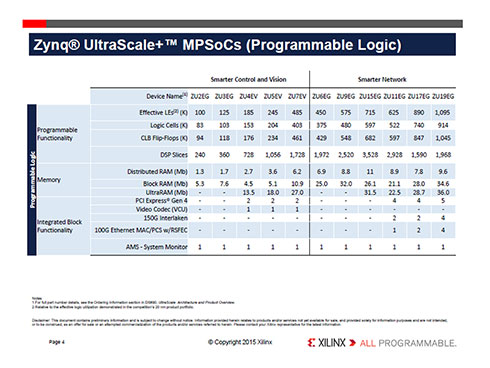

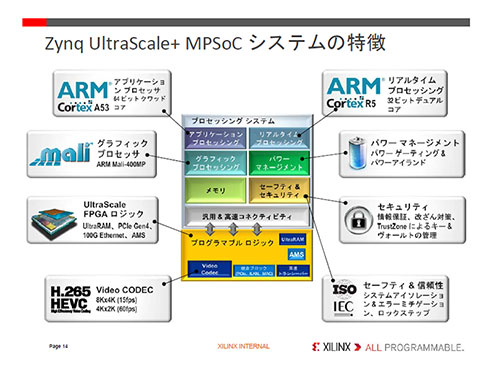

丂Zynq UltraScale亄MPSoC偼64價僢僩偺傾僾儕働乕僔儑儞僾儘僙僢僒乮ARM Cortex-A53僐傾乯偵32價僢僩僨儏傾儖僐傾偺儕傾儖僞僀儉僾儘僙僢僒乮Coretex-R5 MPCore乯丄僌儔僼傿僢僋僾儘僙僢僒乮ARM Mali-400MP乯側偳偺僾儘僙僢僔儞僌僔僗僥儉偲丄H.265偺價僨僆僐乕僨僢僋側偳偺僾儘僌儔儅僽儖儘僕僢僋傪摑崌偟偨儅儖僠僾儘僙僗SoC偩丅

丂僱僢僩儚乕僋張棟偵揔偟偨僐傾傪搵嵹偟偨6惢昳偲丄塮憸張棟偲惂屼偵揔偟偨僐傾傪搵嵹偟偨5惢昳偑梡堄偝傟丄僱僢僩儚乕僋宯張棟偵揔偟偨惢昳偺嵟忋埵昳乽ZU19EG乿偱偼100僊僈價僢僩僀乕僒僱僢僩MAC乮Media Access Control乯偲150僊僈價僢僩/昩偺Interlaken IP乮Intellectual Property乯傪偦傟偧傟4屄搵嵹偟偰偄傞丅塮憸張棟偵揔偟偨惢昳孮偺側偐偱傕乽ZU4EV乿乽ZU5EV乿乽ZU7EV乿偺3惢昳偼丄H.265偺僄儞僐乕僪乛僨僐乕僪婡擻傪搵嵹偡傞丅

丂僓僀儕儞僋僗擔杮朄恖幮挿偺僒儉丒儘乕僈儞巵偼嬤嫷偲偟偰丄乽2015擭偺FPGA斕攧偼夁嫀嵟崅儗儀儖偵側傞偩傠偆乿偲岲挷傪傾僺乕儖偟丄偦偺尨摦椡偲偟偰儚僀儎儗僗偲幵嵹傪嫇偘傞丅傑偨丄乽梡搑暿偵慡偰傪怴婯愝寁偡傞昁梫偼側偔丄偳偺傛偆側傾僾儕働乕僔儑儞偑昁梫偵側傞偐偲偄偆娤揰偱傾僋僔儑儞傪婲偙偟偰偄傞乿偲丄傾僾儕働乕僔儑儞偺娤揰偐傜僾儘僌儔儅僽儖側FPGA偺桪埵惈偼堦憌嵺棫偭偰偄偔偩傠偆偲弎傋偰偄傞丅

丂傑偨丄摨幮FPGA僾儔僢僩僼僅乕儉 儅乕働僥傿儞僌扴摉偺僥傿儉丒僄儖僕儍儀僢僋巵偼16nm UltraScale亄僼傽儈儕偵偮偄偰乽巗応偺梫朷偵墳偊傞僾儘僟僋僩偱偁傝丄乮UltraScale傾乕僉僥僋僠儍傗TSMC偱偺惢憿偵傛傝乯摫擖儕僗僋傕掅偄乿偲傾僺乕儖偟丄壛偊偰丄乽儘僕僢僋僙儖偺悢偱慖傇偺偱偼側偔丄傗傝偨偄偙偲偱慖傫偱傕傜偆乿偙偲偑摨幮偺屭媞偵懳偡傞儊僢僙乕僕偩偲偟偨丅

娭楢婰帠

僓僀儕儞僋僗偑乽嬈奅偱弶傔偰乿20nmFPGA傪検嶻傊

僓僀儕儞僋僗偑乽嬈奅偱弶傔偰乿20nmFPGA傪検嶻傊

僓僀儕儞僋僗偼2014擭12寧18擔乮暷崙帪娫乯丄20nm僾儘僙僗傪巊梡偟偨FPGA乽Kintex UltraScale KU040乿偺検嶻傪奐巒偟偨偲敪昞偟偨丅 僓僀儕儞僋僗偑20nm僾儘僙僗FPGA偺採嫙傪奐巒丄440枩儘僕僢僋偺Virtex傕搊応

僓僀儕儞僋僗偑20nm僾儘僙僗FPGA偺採嫙傪奐巒丄440枩儘僕僢僋偺Virtex傕搊応

僓僀儕儞僋僗偼丄20nm僾儘僙僗偺FPGA乽UltraScale乿偺採嫙傪奐巒偡傞丅儈僢僪儗儞僕偺乽Kintex UltraScale乿僼傽儈儕偲僴僀僄儞僪偺乽Virtex UltraScale乿僼傽儈儕偩丅Virtex UltraScale僼傽儈儕偱偼丄儘僕僢僋僙儖傪440枩屄搵嵹偟偨昳庬傕梡堄偡傞丅 X-fest 2015儕億乕僩丗UltraScale偺徚旓揹椡丄7僔儕乕僘斾偱栺40亾嶍尭

X-fest 2015儕億乕僩丗UltraScale偺徚旓揹椡丄7僔儕乕僘斾偱栺40亾嶍尭

僓僀儕儞僋僗偼丄FPGA媄弍僙儈僫乕乽X-Fest 2015乿乮傾償僱僢僩庡嵜乯偺揥帵夛応偱丄乽Kintex UltraScale乿偲乽Kintex-7乿偺徚旓揹椡斾妑偺僨儌揥帵傪峴偭偨丅傾乕僉僥僋僠儍偺尒捈偟側偳偐傜丄UltraScale偼丄7僔儕乕僘偵斾傋偰徚旓揹椡傪栺40亾嶍尭偡傞偙偲偑偱偒傞丅 帺棩旘峴僋傾僢僪僐僾僞乕偑拡傪晳偆丄僆乕儖僾儘僌儔儅僽儖偺僓僀儕儞僋僗

帺棩旘峴僋傾僢僪僐僾僞乕偑拡傪晳偆丄僆乕儖僾儘僌儔儅僽儖偺僓僀儕儞僋僗

2014擭11寧19乣21擔偺3擔娫丄僷僔僼傿僐墶昹偱奐嵜偝傟傞乽Embedded Technology 2014乛慻崬傒憤崌媄弍揥乿偵偍偄偰丄僓僀儕儞僋僗偼乽Zynq-7000乿乽UltaraScale乿側偳嵟怴偺僾儘僌儔儅僽儖僨僶僀僗傪揥帵偡傞丅

娭楢儕儞僋

Copyright © ITmedia, Inc. All Rights Reserved.

慻傒崬傒奐敪偺婰帠儔儞僉儞僌

- AMD偺PLD帠嬈傪攦廂偟堄婥尙崅偺Lattice Semiconductor偑FPGA嶲擖偱奟偭傉偪偵

- 旕岞奐壔偐傜巒傑傞乽晉巑僜僼僩 Gen.2乿丄AI亊IT亊OT偺梈崌偑彑偪嬝偵

- 嬻慜偺AI僽乕儉両乽擫傕庅巕傕AI乿側尰忬偼崱屻傕懕偔偺偐丠亂慜曇亃

- AI偑壓敿恎偺摦偒傪僒億乕僩丂娯崙敪偺僂僃傾儔僽儖儘儃僢僩乽WIM S乿偑擔杮偵忋棨

- 枩攷傪廔偊偨傾儞僪儘僀僪偨偪偺乽怴偨側廧傑偄乿丂挿扟岺偑昤偔恖偲媄弍偺岎嵎揰

- 擔棫偲擔棫僴僀僥僋偑撈帺僄僢僕AI敿摫懱傪奐敪丄愭抂GPU斾偱張棟岠棪10攞埲忋

- 徚旓揹棳20nA偲1.2V嬱摦傪椉棫偟偨帴婥僗僀僢僠梡AMR僙儞僒乕

- 僷儚乕僨僶僀僗偺懝幐傗壏搙忋徃傪悢昩偱専徹偱偒傞崅懍僔儈儏儗乕僞乕傪岞奐

- 暋悢偺FPGA僼傽儈儕乕偺惢昳儔僀僼僒僀僋儖僒億乕僩傪2045擭傑偱墑挿

- 40戜挻偺儘儃僢僩傪摑崌娗棟偡傞帺棩塣梡僔僗僥儉偑杮奿壱摥

僐乕僫乕儕儞僋