USB 3.0の物理層――スーパースピード伝送の工夫:USB 3.0、スーパースピードを支える技術(2)(1/2 ページ)

USB 3.0の物理層では、大きな伝送路の減衰に対応しながら5Gb/sの高速信号を正しく伝送させるため工夫が必要だ

いま、エレクトロニクス業界で最もホットな話題の1つである「USB 3.0」。本連載では、次世代インターフェイスとして期待されているこの高速通信規格の概要から、物理層を中心に技術的な面まで掘り下げて解説していく。(編集部)

伝送路の減衰

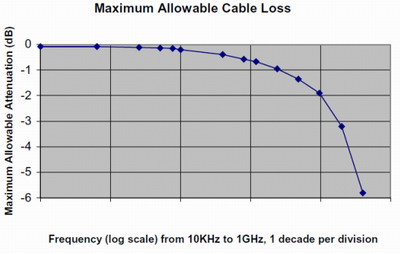

前回概要でお伝えしたように、USB 3.0、スーパースピードの物理層はPCI Express Gen2と多くの共通点を持っています。大きな伝送路の減衰に対応し5Gb/sの高速信号を正しく伝送させるための工夫が必要です。図1にはUSB 2.0規格のケーブルの減衰特性を示しています。

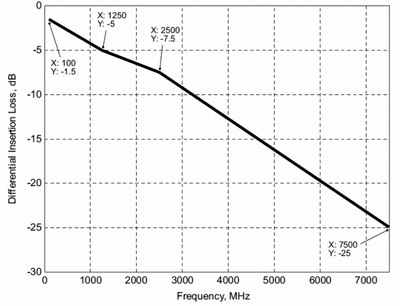

このように800MHzを超えると大きな減衰があることが図1でも分かります。当然ながら5Gb/sのスーパースピードの信号伝送を安定的に行うことは無理だということが容易に想像することができます。従ってスーパースピードではUSB 2.0とは別の伝送線を使用します。図2にはスーパースピードのケーブル減衰特性を示しています。

1.25GHzで5dBの減衰となっているようにUSB 2.0のケーブルと比べ明らかに良好な高周波特性を有しています。しかしながら5Gb/sの最速データ信号の基本波である2.5GHzで7.5dB、その3次高調波の7.5GHzでは25dBもの減衰を示します。このように減衰特性は、周波数が高いほど減衰が大きくなるローパスフィルタのような効果を持ちます。このような環境下では、データ信号がパターンによって、その減衰量を変えるのでパターン依存と呼んだり、符号間干渉、英語でInter-Symbol-Interference(ISI)と呼ばれます。

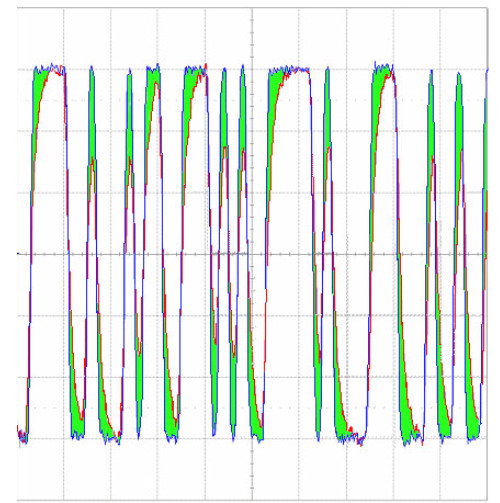

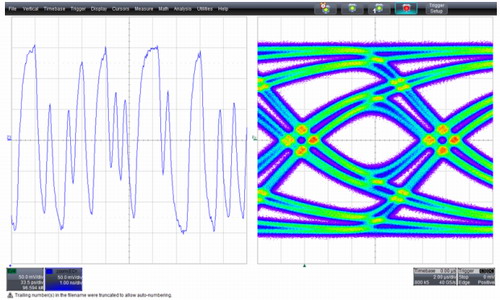

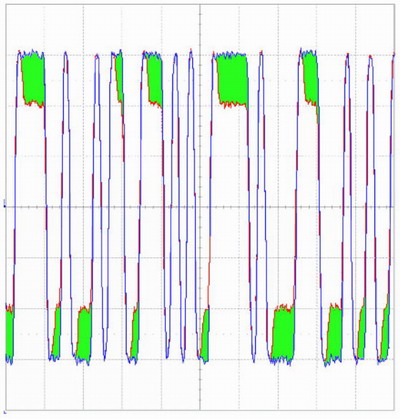

図3は、符号間干渉の影響を示すために、符号間干渉のない理想的な波形と、符号間干渉が起きた波形を重ね合わせ、減衰した部分を塗りつぶしています。短いパルスが減衰しているだけではなく幅広いパルスの減衰もエッジの直近が大きく、エッジから離れるに従って減衰が小さくなっています。その結果、図4に示したようにアイパターンが乱れ、開口が小さくなるだけでなく、クロスポイントが4つに分かれて見えるようにデタミニスティックジッタが顕著になります。

デエンファシス

このように、あらかじめ減衰する部分とその大きさが推定できていると、送信器の出力を調整して補正することが可能です。つまり減衰する部分をあらかじめ強化して送信することが考えられます。これはプリエンファシスと呼ばれる方式ですが、高周波成分を強調するのはEMIの観点からは望ましくありません。そこで、プリエンファシスと同様に符号間干渉の影響を補正しながら良好なEMIを保つ方式としてデエンファシスが採用されています。これは、減衰する高周波成分に合わせて低周波成分をあらかじめ減衰させておくという方式です。

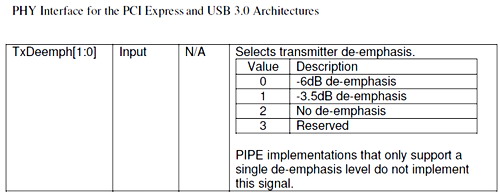

図5にデエンファシスを行う前と後の波形を重ね合わせ、減衰させる部分を塗りつぶしています。このように送信側で波形を操作することで伝送線の減衰による符号間干渉の補正を行うことができます。前回紹介したPHY Interface For the PCI Express and USB 3.0 Architectures Version 3.0を見てみると、表1のようにデエンファシスには−3.5dBと−6dBが選択できるようになっていますが、−6dBが選択できるのはPCI Expressモード時のみで、USB 3.0モードでは−3.5dBだけが許されます。同じ5Gb/sの高速信号を取り扱い、最大3メートルのケーブルの使用を認めていて、より大きな減衰が予測され るにもかかわらず、PCI Expressよりも少ないデエンファシスにしているのには理由があります。

伝送路の条件変動

PCI ExpressとUSB 3.0スーパースピードは、その使用環境の違いにより、いくつかの技術的機能の差異があると話をしました。PCI Expressは、基本的にパソコン内部バスであるので使用条件などで伝送線路が変更されることはありません。従って、設計段階で想定される伝送線路に対して最適化すればよいということになります。しかしながら、USB 3.0では、USB 2.0との下位互換性がうたわれており、USB 2.0と同様の使用環境を想定しています。つまり、パソコンの外部周辺機器を自由にかつ簡便に接続することが必要になります。これを実現するには、接続する機器によって大きく変わる伝送路に応じて信号品質の最適化を行わなければなりません。

USBメモリのようにAコネクタに直結する場合と、最大3メートルのケーブルで 接続する場合では、伝送路の減衰が大きく異なります。また、USB 2.0と同様の利用環境を想定しているために、図6のように現行同様にパソコンの前面パネルおよび背面パネルにUSBコネクタを配置することが想定されます。この場合に、前面パネルと背面パネルではプリント基板のトレース長が大きく異なり、伝送路の減衰特性がここでも大きく異なることが分かります。リアパネルに3メートルケーブルで機器を接続した場合にも、フロントパネルに直結でメモリを接続した場合にも同様に安定した通信を確保しなければなりません。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 4年目を迎えた「小さく始めるAIパビリオン」、マイコンよりMPU多めの構成に

コーナーリンク

図1 USB 2.0規格のケーブルの減衰特性

図1 USB 2.0規格のケーブルの減衰特性 図2 スーパースピードのケーブル減衰特性

図2 スーパースピードのケーブル減衰特性 図3 塗りつぶされた部分が減衰

図3 塗りつぶされた部分が減衰 図4 アイパターンが乱れている

図4 アイパターンが乱れている 図5 デエンファシス実施前後の波形を重ね合わせ、減衰させる部分を塗りつぶしている

図5 デエンファシス実施前後の波形を重ね合わせ、減衰させる部分を塗りつぶしている 表1 PHY Interface For the PCI Express and USB 3.0 Architectures

表1 PHY Interface For the PCI Express and USB 3.0 Architectures 図6 USBコネクタの想定配置例

図6 USBコネクタの想定配置例