SoC設計者がIPに関心を持つべきタイミング:SYSTEM DESIGN JOURNAL(1/4 ページ)

SoCが自律走行車やIoTなどの分野に進出しようとしていますが、求められる要件は分野によって大きく異なります。その結果、SoC開発者がIP(Intellectual Property)を評価・統合する方法に変化が見られます。

System-On-Chip(SoC)が自律走行車やIoTといった次の大ブームをもたらす市場に進出する中、SoC設計者は環境、ライフサイクル、信頼性、セキュリティなど、民生アプリケーションや通信アプリケーションでは全く経験したことがない新しい種類の課題と要件に直面しています。

その結果、SoC開発者がIP(Intellectual Property:知的財産、回路情報)を評価して統合する方法が変化しています。さらにはSoCのデータシートに決して表れない問題により、開発者がIPに関して決定したことがその顧客であるシステム開発者に大きな影響を及ぼしています。Design&Reuse IP/SoC Conferenceにて発表された論文では、これら隠れた問題の幾つかにスポットライトが当てられました。

常に正常動作することを要求される車載用機器

乗用車やその他車両のシステムアーキテクチャは、抜本的な転換期を迎えています。今日の自動車のブロック図にはそれぞれセンサーやアクチュエータに接続され、業界標準および独自規格のバスやリンクが蜘蛛の巣のように絡み合って車両の残りの部分とつながり、数百もの単一機能のMCU群が示されています。

この絡み合った状態では、車両全体の状況を1つのプロセッサで明確に把握することはできません。そのため、冗長化やエラーリカバリの機会が減少します。また、自動車メーカーにとっては、この手法ではケーブル配線のコストと重量が大幅に増加することが差し迫った懸念になっています。

今後、状況は変わるでしょう。OmniPhyの最高技術責任者であるClaude Gauthier氏は、「BMWやJaguarなどの高級ブランドを皮切りに、アーキテクチャは単一のイーサネット・バックボーンに進化しつつあります。当初は、単一のツイストペアを通る工業用/車載機器用プロファイルである100Mb/secのIEEE 802.3bwや1Gbの802.3bpがベースになります」と述べています。

この変化により小型MCUの多くは姿を消すこととなり、代わりに登場するのは、センサーデータと制御アクチュエータを融合し、ローカル処理を中央電子制御ユニットからのサポートと組み合わせたミックスド・シグナルSoCです。このシステムの心臓部は、サーバのCPUチップに似たヘテロジニアス・マルチコアSoCです。

これらのSoCによってアーキテクチャに新しい課題が突きつけられることはありません。しかし、そのような自動車向けチップを作り出すことは、これまで自動車業界を相手にしたことがなかったSoCデザインチームにとって新しい経験です。自動車業界という、オートモーティブ・グレードの小型MCUとミックスド・シグナル・コンポーネントが支配していた世界で、SoCだけを扱うことになります。

Gauthier氏は「これは別の市場です。認証には非常に長い期間を要するのに、仕様は非常に短期間で変更されます。規格はまだ模索中です」と警告しています。

この長期にわたる認証プロセスでの問題の多くから、SoCデザインチームとそのIPベンダーの間に新しい議論が起きるでしょう。802.3bwイーサネットインタフェースのような新しい機能の登場が当然予想されますが、新しい温度範囲、新しい信頼性要件、さらにAEC-Q100のような新しい品質基準も生まれるでしょう。

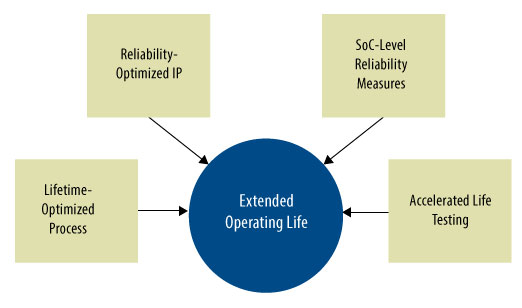

Q100は既知のIC故障モードを中心に設計された、自動車業界で要求される長い製品寿命でのチップ故障率を予測するための一連のストレス試験です。この試験の多くはパッケージングの故障モードに焦点を当てていますが、SoC開発者の直接的な懸念事項であるダイのエージング問題を調べる試験もあります。

このカテゴリ固有の試験には、エレクトロマイグレーション、時間に依存する絶縁破壊、ホットキャリア注入、負バイアス温度不安定性、ストレス移行などのチェックがあります。これらの試験に合格するには、SoCのファウンドリが各種プロセスに対するQ100認証を取得する必要があります。

一方、IPベンダーもまた、Q100認証を取得したバージョンのプロセスで行ったデザインが試験に合格できることを保証する必要があります。インフォテイメント以外の車載機器はSoCにとって新興市場であるため、シリコンで実証されたIPコアでもQ100認証プロセスで構築されたシリコンのQ100審査を受けていない可能性があります。

AEC-Q100はSoCのハードウェア障害の可能性を調査します。しかし、車載機器の設計者が関心を深めているのは、デザインエラーという信頼性の別の側面です。ISO 26262などの機能安全規格は、正式に検証された、またはフィールドで実証されたコンポーネントとソフトウェアの使用を義務付けることを目指しています。その結果、車載機器用SoCのユーザーは、SoC設計者がデザインをどのように検証したかに注目し始めています。そして、この好奇心によって厄介な問題が起きています。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

人工知能の奇跡的な復権

人工知能の奇跡的な復権

囲碁王者への勝利を果たすなどAI(人工知能)への注目は依然として高くありますが、研究史を知る身からすれば、AIへの興奮はジェットコースターのようなものであるとも感じられます。多岐にわたる成果を挙げ始めた現代のAIは何が違うのでしょうか。 中世史に学ぶ、組み込みシステムのセキュリティモデル

中世史に学ぶ、組み込みシステムのセキュリティモデル

セキュリティの確保は重要ですが、リソースや利便性との兼ね合いも求められます。組み込みシステムのセキュリティ確保について、中世の城の防衛策を例に考察します。 WoT(Web of Things)と化すIoTに待ち受ける、分断された未来

WoT(Web of Things)と化すIoTに待ち受ける、分断された未来

さまざまな企業や勢力がIoTを目指していますが、残念ながら勢力ごとの対話はほぼ存在していません。Web技術を共通言語とし、IoTを「WoT(Web of Things)」とすることで妥協点を見いだそうという動きはありますが、成功するかは不透明と言わざるを得ません。 「SoC」or「SoC」?統合へのさまざまな道

「SoC」or「SoC」?統合へのさまざまな道

1つのダイに複数機能を実装するSoC(System on Chip)化の波は高まるばかりです。アーキテクトはダイ間接続とマルチダイパッケージングの動向に注意を払い、コストや消費電力、将来性までも視野に入れた選択をしなければなりません。 組み込みコンピューティングに向けた、ハードウェアアクセラレーションの選択肢

組み込みコンピューティングに向けた、ハードウェアアクセラレーションの選択肢

組み込みコンピューティングを加速させるハードウェア・アーキテクチャとは何でしょうか。DSP?GPU?それともメニーコアでしょうか。どのアプローチが最も適するのかを考察します。 FinFET革命がコンピュータアーキテクチャを変える

FinFET革命がコンピュータアーキテクチャを変える

FinFETの登場により、ムーアの法則はまだ継続される見通しです。ですが、それで全てが解決するわけではありません。FinFETの登場が、大きなSoCを自律的な機能ブロックに分割するという方向に導く結果となるでしょう。 サブシステムIPがチップの境界を越える

サブシステムIPがチップの境界を越える

サブシステム規模のIP(サブシステムIP)はSoCはもちろん、FPGAにまでも影響を与えています。素晴らしい取り組みですが、さまざまな注意点も存在します。スムーズな実装を行うための4つの注意点について述べます。