FinFET革命がコンピュータアーキテクチャを変える:SYSTEM DESIGN JOURNAL(1/4 ページ)

FinFETの登場により、ムーアの法則はまだ継続される見通しです。ですが、それで全てが解決するわけではありません。FinFETの登場が、大きなSoCを自律的な機能ブロックに分割するという方向に導く結果となるでしょう。

20nmCMOSロジックプロセスノードに始まる「FinFET」の出現によって、ムーアの法則が正しく守られることになりました。

プレーナMOSFETをスケーリングし続ける能力が弱まり始めたちょうどそのとき、FinFETの極めて優れたチャネル制御が救いの手を差し伸べ、リーク電流を減らして電圧スケーリングを継続する道が開かれました。このタイムリーな出現によって、2015年2月に行われたDesignAutomationConferenceの基調講演でVivekSingh(ビベック・シン)氏が述べたよう、インテルは14nmノードでもトランジスタの速度と消費電力カーブの着実な改善を維持することが可能になりました。

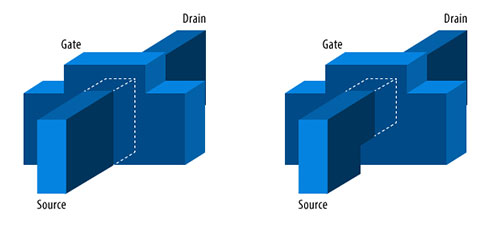

トランジスタ本体を覆うゲートの3辺がフィン(ひれ)状でありリーク電流を制御するため、デバイス設計者は自由に動作電圧と限界寸法を減らし続けることができます(その形状からインテルはトライゲートと呼びます)。ますます進むデバイスエンジニアリングと新材料に支えられたものとはいえ、この自由は14nmまで続き、さらに10nmとその先でも約束されています。

例えば、TSMCのR/D担当バイスプレジデントであるYJ Mii(YJミー)氏は直近のTSMCテクノロジーシンポジウムで、同社が10nmの先においてもFinFETとその近い親類である全周ゲートFET(図1)を検討していること、ただし、恐らくはゲルマニウム、またはインジウム、ガリウム、ヒ素化合物のフィンを付けると明らかにしました。

全てが良いことばかりではない

トランジスタのサイズと性能は再びスケーリングし始めましたが、オンチップインターコネクトの状況はそれほど有望ではありません。最も根本的なレベルにおいてFinFETは本質的に寄生容量が大きく、理論的に向上した回路速度―消費電力の関係の一部を相殺します。さらに、信じられないほど小型化するトランジスタと歩調を合わせて小さくなるコンタクト、ローカルインターコネクト、下層の金属レイヤーは、それぞれ独自の問題にぶつかっています。

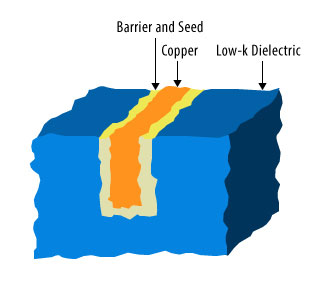

例えば、コンタクトのピッチをトランジスタの間隔に合わせて狭めると、コンタクトの直径も小さくしなければなりません。しかし、コンタクト充填(じゅうてん)材を周囲の誘電体から隔てるライナーはそれほど薄くなりません。その上、穴のエッジ粗さは魔法のようには改善されません。従って、コンタクト金属用に残された領域が穴径よりもさらに急速に減少し、直列抵抗値が急激に増加します。この問題は下層レベルの銅インタコネクト線においてさらに深刻です。この線はシードとバリアのレイヤーを小型化できないために、徐々に狭められます(図2)。

SRAM IPベンダーのSurecoreによれば、重要なデザインでのインターコネクトインピーダンスは40nmにおいて問題になり始めていたとのことです。同社は、とりわけ長い金属経路をなくすことによって、SRAMで測定したTSMC40LPの動的消費電力を1/2未満に低減させました。

ですが28nmより細くなると、寄生容量に抵抗値が加わって真のRC問題が発生します。Surecoreの最高技術責任者であるDuncanBremner(ダンカン・ブレムナ)氏は、「28nmを過ぎると、抵抗値が大きく影響し始めます。さまざまなパスでRCのマッチングを始めて、デジタル回路の深刻なスキュー問題を回避する必要があります」と警告しています。

プロセスのばらつきが増えていることも問題です。トランジスタの実際の形状、チャネルドーピングレベル、インターコネクトの形状は、ロット間、ウェハ間だけでなく1つのダイの表面全体にわたって変動します。潜在的に大きな動作温度の差とその結果としてのダイ全体でのエージング速度の差に加えて、興味深い状況があります。

同じチップ上で、共通のクロック周波数で動作する別の部分が異なる電圧を必要とする場合があります。あるいは、異なるクロック周波数で動作する別の部分を、最小消費電力で動作させる場合があるのです。

肯定的に見ると、次世代FinFETプロセスはトランジスタの集積度と速度―消費電力積に極めて実質的な利点をもたらします。否定的な面では、インターコネクトの容量と抵抗値が深刻な問題になりつつあります。同一ダイ上のプロセスのばらつきでさえ、マルチコーナー解析とガードバンディングが多くを諦める状況に達しました。これらの要素がシステムアーキテクトの視界に入り始めました。

関連記事

サブシステムIPがチップの境界を越える

サブシステムIPがチップの境界を越える

サブシステム規模のIP(サブシステムIP)はSoCはもちろん、FPGAにまでも影響を与えています。素晴らしい取り組みですが、さまざまな注意点も存在します。スムーズな実装を行うための4つの注意点について述べます。 畳み込みニューラルネットワークの使い方、分かりますか?

畳み込みニューラルネットワークの使い方、分かりますか?

畳み込みニューラルネットワークとは何でしょうか。学問の世界から現実の世界に登場しつつあるこれは、さまざまな組み込みシステムに利用される可能性が高く、大いに関心を持つべきです。 組み込みにおけるコンピュータビジョンを整理する

組み込みにおけるコンピュータビジョンを整理する

画像認識(コンピュータビジョン、マシンビジョン)の需要は高まっており、その方法はさまざまです。画像による入力を有用なものとする実装方法について分類と整理を試みます。 モノのインターネットを再考する

モノのインターネットを再考する

IoTがその現実性について語られるようになった2015年、その基本概念を再考する機運が高まっています。「センサー」「仮想化」「フォグ」などの観点から、IoTを再考してみましょう。 コンピュータ・アーキテクトのためのモーター制御

コンピュータ・アーキテクトのためのモーター制御

「モーターを制御する」。一見すると簡単な課題に思えますが、その原理や課題、現状を再確認すると、リアルタイムシステムアーキテクチャの今後の方向性を示していることが分かります。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 40台超のロボットを統合管理する自律運用システムが本格稼働

- 4年目を迎えた「小さく始めるAIパビリオン」、マイコンよりMPU多めの構成に

コーナーリンク

図2.下層金属レイヤ-の銅インタコネクト線は、線-エッジ粗さとバリア――シードのレイヤーのために狭められてきています

図2.下層金属レイヤ-の銅インタコネクト線は、線-エッジ粗さとバリア――シードのレイヤーのために狭められてきています