FinFET革命がコンピュータアーキテクチャを変える:SYSTEM DESIGN JOURNAL(4/4 ページ)

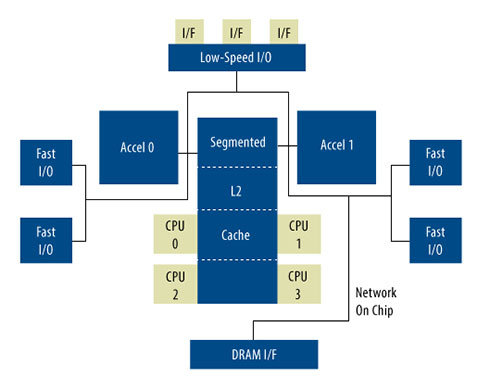

そのようなネットワークは、ネットワーク合成ツール、ライブラリ、検証IP(Intellectual Property)を含むパッケージとしてすぐに使用できます。NoCは、単純にブロック相互間のタイミングを分離することによって、デザインの、ダイ上のばらつきによるもの以外の全てを実現します(図3)。

しかし、全ての非同期メッセージ伝達によってレイテンシが加わっても、結果的にデザインが性能要件を満たすことができることを確認する必要はもちろんあります。メッセージベースのネットワークは、高速ストリーミングデータフローなど、幾つかの状況を扱うには最善の方法でない場合があります。

「SoCの機能ブロック分割」という潮流

プロセスや熱、エージングのばらつきに対処するべくトランジスタを配置する上で、もう1つのポイントが重要になってきています。

先進的なSoCデザインは、隣接ブロックと同期しない多数の大きく異なった独立ブロックに分解されます。これらのブロックにはそれぞれ、独自のシステム管理ニーズがあります。それぞれが、温度や遅延の測定値に基づく定期調整と電源管理方式を必要とする、多くの独立した電圧ドメインを持つことがあります。

同様に、各ブロックがローカルリキャリブレーションを必要とする高精度アナログ回路やトランシーバーを持つこともあります。ブロックに大量のメモリがあれば、定期的なスクラビングによってソフト・エラーを抑制する必要がある場合があります。さらに、チップ上の他の部分と共有しない、あるいは、他の部分を頼りにしないセキュリティ(認証および暗号化)ニーズを持つブロックもあり得ます。

その結果、一部のアーキテクトはローカルなブロックレベルのシステム管理プロセッサを実装しています。これらのMCUは、上記の問題と電源投入およびシャットダウン中の電源レールのシーケンシングなどの特別なニーズを扱うことができます。

豊かなトランジスタバジェット、ますます問題になるインターコネクト、増え続けるダイ上プロセスのばらつき、という3つの要素の全てが、大きなSoCを自律的な機能ブロックに分割するという方向に働きます。

これらのブロックは独自のタイミングを持ち、電源投入時または動作中に動作周波数と電圧の選択を独自に決定することが可能です。さらに、これらのブロックは独自の内部システム管理機能と、恐らく電圧安定化機能を備えることがますます増えるでしょう。

機能ブロックの自律性がこのように高まると、今日のデザインに起きている問題を解決するだけでなく、モノリシック回路とマルチダイ回路の区別が曖昧になり始める将来に向かって、アーキテクトが準備をすることができます。

関連記事

サブシステムIPがチップの境界を越える

サブシステムIPがチップの境界を越える

サブシステム規模のIP(サブシステムIP)はSoCはもちろん、FPGAにまでも影響を与えています。素晴らしい取り組みですが、さまざまな注意点も存在します。スムーズな実装を行うための4つの注意点について述べます。 畳み込みニューラルネットワークの使い方、分かりますか?

畳み込みニューラルネットワークの使い方、分かりますか?

畳み込みニューラルネットワークとは何でしょうか。学問の世界から現実の世界に登場しつつあるこれは、さまざまな組み込みシステムに利用される可能性が高く、大いに関心を持つべきです。 組み込みにおけるコンピュータビジョンを整理する

組み込みにおけるコンピュータビジョンを整理する

画像認識(コンピュータビジョン、マシンビジョン)の需要は高まっており、その方法はさまざまです。画像による入力を有用なものとする実装方法について分類と整理を試みます。 モノのインターネットを再考する

モノのインターネットを再考する

IoTがその現実性について語られるようになった2015年、その基本概念を再考する機運が高まっています。「センサー」「仮想化」「フォグ」などの観点から、IoTを再考してみましょう。 コンピュータ・アーキテクトのためのモーター制御

コンピュータ・アーキテクトのためのモーター制御

「モーターを制御する」。一見すると簡単な課題に思えますが、その原理や課題、現状を再確認すると、リアルタイムシステムアーキテクチャの今後の方向性を示していることが分かります。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- 40台超のロボットを統合管理する自律運用システムが本格稼働

コーナーリンク