補正不要で低ジッタと低スプリアスを両立する新方式PLLを開発:組み込み開発ニュース

東京大学は、次世代無線通信に向けたPLLの新方式を開発した。157フェムト秒の低ジッタと−73dBcの低スプリアスを同時に達成し、高速無線通信における周波数シンセサイザー技術としての応用が見込まれる。

東京大学は2026年2月14日、回路性能の補正を必要とせずに、低ジッタと低スプリアスを同時に実現する分数分周PLL(位相同期回路)の新方式を開発したと発表した。高速無線通信に必要不可欠な低雑音の周波数シンセサイザー技術として、次世代無線通信規格への応用が見込まれる。

従来の分数分周PLLでは、量子化雑音を抑制するためにデジタル時間変換器を用いた補正が一般的だが、補正処理によるロック時間の長期化が課題となっていた。

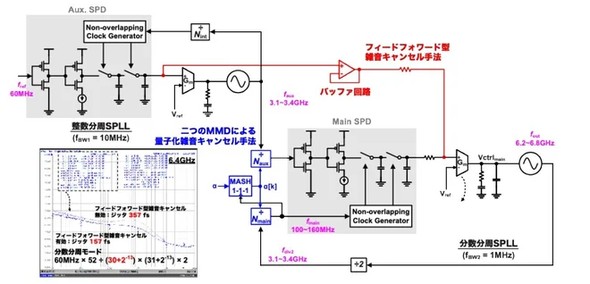

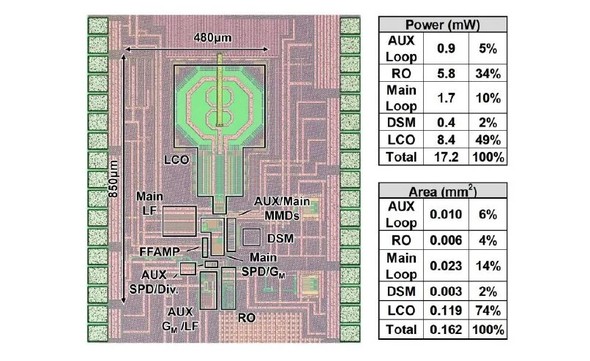

今回開発した回路は、2段のPLLを組み合わせたカスケード構造を採用。主要な技術として、共通のデルタシグマ変調器(DSM)で制御された2つのマルチモジュラス分周器(MMD)を用いる量子化雑音キャンセル手法を導入した。これにより、後段PLLに入力される量子化雑音を、分周比Nに対して1/Nに低減することに成功。この手法は環境依存性や非線形性に影響されないため、補正処理を介さずに安定した雑音低減が可能となる。

さらに、実装面積の削減と低雑音化を両立するため、フィードフォワード型雑音キャンセル手法を適用した。初段PLLに小面積なリング型発振回路を採用し、その雑音成分を後段PLLの出力で打ち消す構成とした。サンプリング位相検出器(SPD)の位相検出器としてのゲインが入力周波数に応じて変化するという特性を活用し、分周比の設定に依存せずロバストに雑音をキャンセルできる仕組みを構築している。

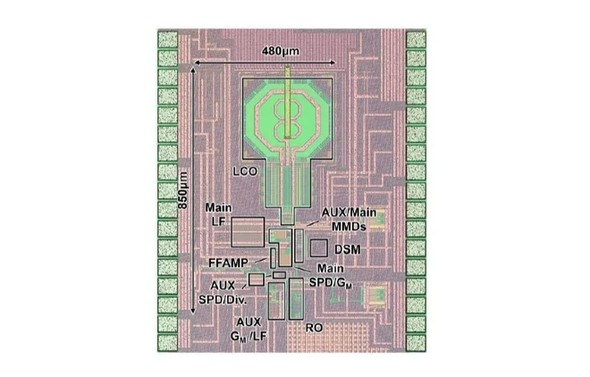

65nm CMOSプロセスで試作されたチップによる実測では、157フェムト秒のジッタ性能と−73dBcのスプリアス性能を実証した。補正不要で出力周波数や分周比に依らずに安定動作するため、次世代の高速、低遅延通信を可能にする高精度な基準信号生成技術として、社会実装に向けた研究開発を進めていく。

関連記事

FPGAの内蔵温度センサーから値を得る

FPGAの内蔵温度センサーから値を得る

アルテラのFPGA「MAX 10」には温度センサーが内蔵されており、自身の温度を測定可能だ。メガファンクション「ALTPLL」を使い、内蔵センサーからの値を得るまでを試みる。 CPU・MPUはどうやって動く? 〜 発振器のナゾ

CPU・MPUはどうやって動く? 〜 発振器のナゾ

発振器とは、MPUを動作させるための同期信号(クロック)を発生させる回路。具体的にどんな役割を担っているのか解説しよう なぜいま、正しいタイミング解析が重要なのか?

なぜいま、正しいタイミング解析が重要なのか?

複雑な回路でも間違いなく解析したい。そんな設計者のために、タイミング解析とSDCフォーマットによるタイミング制約の方法を伝授!! SDCを使ったタイミング制約を押さえよう

SDCを使ったタイミング制約を押さえよう

回路設計におけるタイミング制約に悩む人も多いだろう。今回は実際の回路を例に取り、SDCを使ったタイミング制約を解説する。 ソース・シンクロナス・インターフェイスの制約を学ぶ

ソース・シンクロナス・インターフェイスの制約を学ぶ

今回はデータをクロックとともに送信する「ソース・シンクロナス方式」のインターフェイスのタイミング制約を解説する。 低価格FPGAを用いた文字認識AI推論の全体像

低価格FPGAを用いた文字認識AI推論の全体像

FPGAにニューラルネットワークを実装するプロセスを学ぶ本連載。第1回では、連載の狙いや、文字認識AIモデルの概要、どのようにFPGA上で文字認識を行うかなど全体の流れを紹介する。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 40台超のロボットを統合管理する自律運用システムが本格稼働

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

コーナーリンク