Rapidusが半導体回路の設計期間を半減する支援ツールを投入、一部は無償提供へ:SEMICON Japan 2025(2/2 ページ)

無償ツールの提供でファウンドリー利用の高いハードルを下げる

Rapidus エンジニアリングセンター設計技術統括部ディレクターの鶴崎宏亀氏は「一般的な半導体製造の評価指標は、処理性能(Performance)、電力(Power)、面積(Area)から成るPPAが基準になっている。2nmプロセスで製造することになる大規模な半導体チップであるAIアクセラレーターやCPUの場合、PPAだけでなく、コスト(Cost)とタイムトゥマーケット(Time to Market)を含めたPPACTMが重要になっている」と述べる。

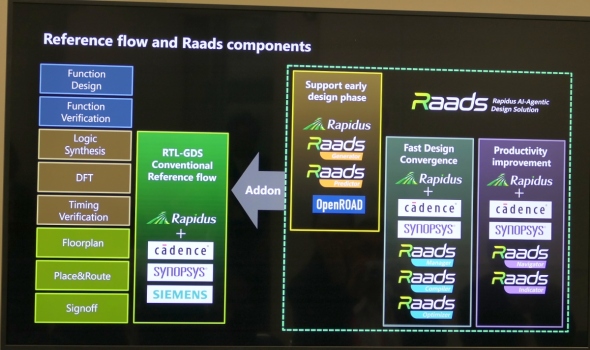

ただし、Rapidusはファウンドリーであり半導体回路設計は顧客が行うことになる。同社はその半導体回路設計を短期間で完了できるように、基準となる参照設計フローと併せて、オプションの形でRaadsのツール群を提供する。これらのツール群を活用することで設計期間の50%削減と、それによる設計コストの30%削減が可能になることを想定している。

Raadsは、半導体の回路設計プロセスとRapidusの参照設計フローに対応する3つの領域で7つのツールを用意している。

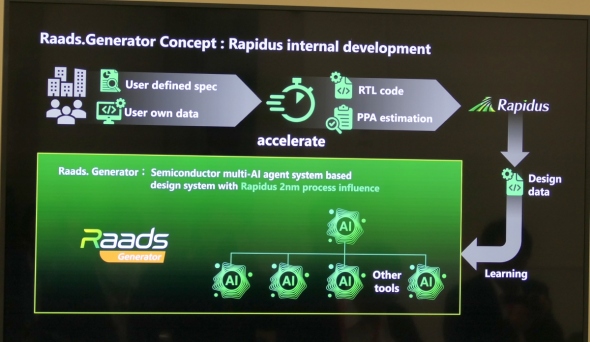

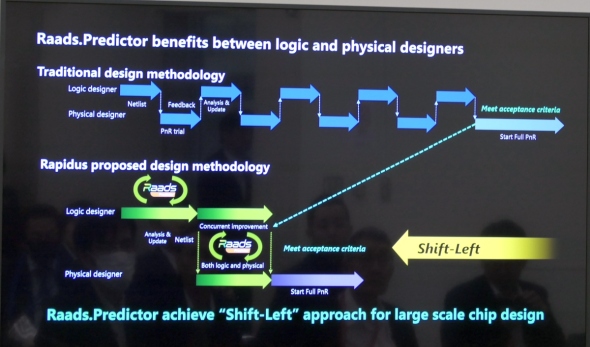

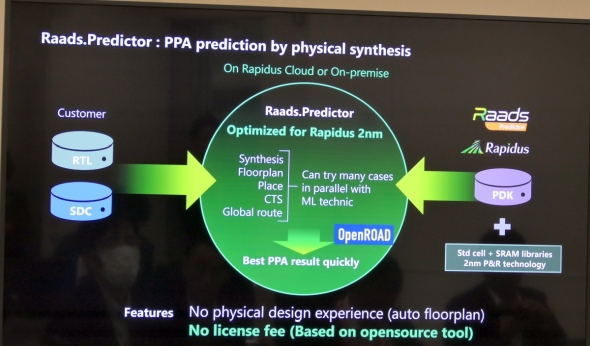

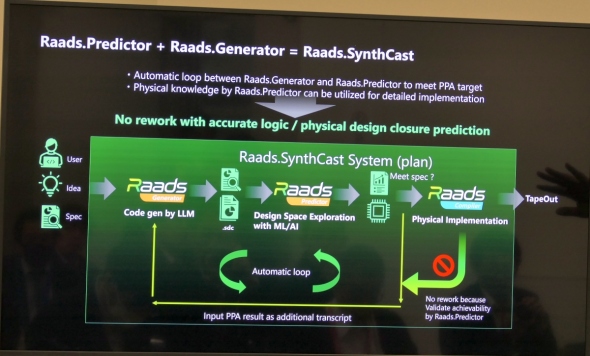

論理設計から物理設計の出力に対応する上位設計のプロセスに対応するのが「Raads Generator」と「Raads Predictor」である。Raads Generatorは、LLM(大規模言語モデル)ベースのEDAツールであり、設計者が半導体の仕様を入力するとRapidusの2nmプロセスに最適化されたRTL設計データを出力する。一方、Raads Predictorは、RTLのデバッグおよび物理設計/配置配線の最適化ツールでPPA予測を短期間で実現できる。

なお、Raads GeneratorとRaads Predictorはオープンソースソフトウェアとして公開する予定であり、同じくオープンソースソフトウェアのEDAツール「OpenROAD」と組み合わせれば、Rapidusの2nmプロセスに合わせた半導体回路設計の最適化を無償で行えるようになる。「Raads Predictorは論理設計から自動で物理設計を出力する機能を備えているので、物理設計に関する経験がなくても半導体回路設計を試せるものになっている。アカデミアやスタートアップにとってファウンドリー利用のハードルは高いが、まずはこの無償のツールで半導体回路設計を簡単に試せる環境を整備して、そのハードルを下げたいと考えた」(石丸氏)という。

より具体的なレイアウトと関わる領域では、設計期間の短縮と歩留まり向上に分けてツールを提供する。設計期間の短縮ではML(機械学習)/AIを活用したツールである「Raads Manager」「Raads Compiler」「Raads Optimizer」、歩留まり向上ではLLMを活用し設計者の品質保証や支援を行うとともに設計課題に対する解決策を導出する「Raads Navigator」「Raads Indicator」を提供する。これらは、ケイデンス(Cadence Design Systems)やシノプシス(Synopsys)のEDAツールのプラグインとなる。

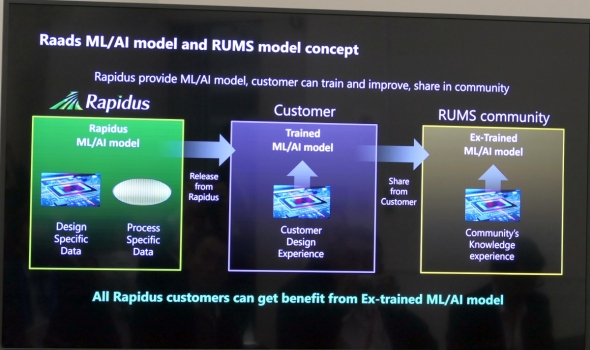

なお、設計期間の短縮に用いるML/AIモデルについては、Rapidusが提供するモデルを基に顧客の設計の手法やノウハウなどを追加学習した新たなML/AIモデルを、Rapidusの顧客全員がアクセスできるRUMSコミュニティーで共有するコンセプトを検討している。

また、将来的にはRaads GeneratorとRaads Predictor、Raads Compilerを組み合わせた「Raads SynthCast System」を構築することで、ターゲットとするPPAに合わせて半導体回路設計の最適化ループを回して、手戻りすることなくフォトマスク製造のためのテープアウトまで進めることも想定している。

関連記事

ラピダス半導体工場の現状と今後、パイロットライン立ち上げ開始も「まだ一合目」

ラピダス半導体工場の現状と今後、パイロットライン立ち上げ開始も「まだ一合目」

Rapidus(ラピダス)は、北海道千歳市で進む半導体工場「IIM(イーム)」建設の現状と今後の計画について説明した。 2nmプロセスGAAトランジスタの試作ウエハーで動作を確認

2nmプロセスGAAトランジスタの試作ウエハーで動作を確認

Rapidusは、北海道千歳市にある最先端ファウンドリ「IIM-1」で、2nm GAAトランジスタの試作ウエハーで動作を確認したと発表した。これは、同社が掲げる2027年の量産開始に向けた重要なマイルストーンとなる。 Rapidusと連携深めるテンストレント、東京オフィスで半導体エンジニアを積極育成

Rapidusと連携深めるテンストレント、東京オフィスで半導体エンジニアを積極育成

テンストレントが新たに入居した東京オフィスで会見を開き、来日した同社 CEOのジム・ケラー氏が2nmプロセス半導体の製造で協業しているRapidusとの関係や、日本国内における今後の取り組みなどについて説明した。 Rapidusは新工場稼働間近、クエスト・グローバルとの協業でRUMSモデルが完成へ

Rapidusは新工場稼働間近、クエスト・グローバルとの協業でRUMSモデルが完成へ

Rapidusとクエスト・グローバルが2nmプロセスのロジック半導体に関するMOC(協力覚書)を締結した。Rapidusがクエスト・グローバルの新たなファウンドリーパートナーになるとともに、クエスト・グローバルはRapidusの2nmプロセスを用いて半導体を製造する顧客に対して半導体設計に関する人材やエンジニアリングソリューションを提供する。 PFNの次世代MN-CoreをRapidusが製造、さくらインターネットと国産AIインフラ構築

PFNの次世代MN-CoreをRapidusが製造、さくらインターネットと国産AIインフラ構築

Preferred Networks(PFN)、Rapidus、さくらインターネットの3社は、グリーン社会に貢献する国産AIインフラの提供に向けて基本合意を締結したと発表した。 IBMとRapidusが2nmプロセス半導体の量産に向け「重要なマイルストーンに到達」

IBMとRapidusが2nmプロセス半導体の量産に向け「重要なマイルストーンに到達」

IBM ResearchとRapidusは、新たなエッチングプロセスであるSLR(Selective Layer Reductions:選択的薄膜化)を用いて、マルチ閾値電圧を持つナノシートGAAトランジスタを製造できるようになったと発表した。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- 40台超のロボットを統合管理する自律運用システムが本格稼働

コーナーリンク

Rapidusの鶴崎宏亀氏

Rapidusの鶴崎宏亀氏